Home » Innovative DRAM » RPC DRAM

|

|

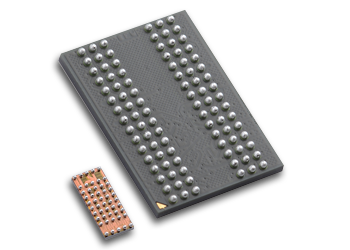

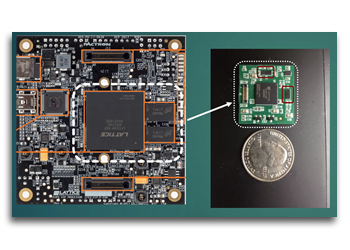

| RPC DRAM in WLCSP (Left) vs DDR3 in 96 BGA (Right) | 0.8 mm pitch: ECP5 + DDR3 (Left), 0.5 mm pitch ECP5 + RPC (Right) |

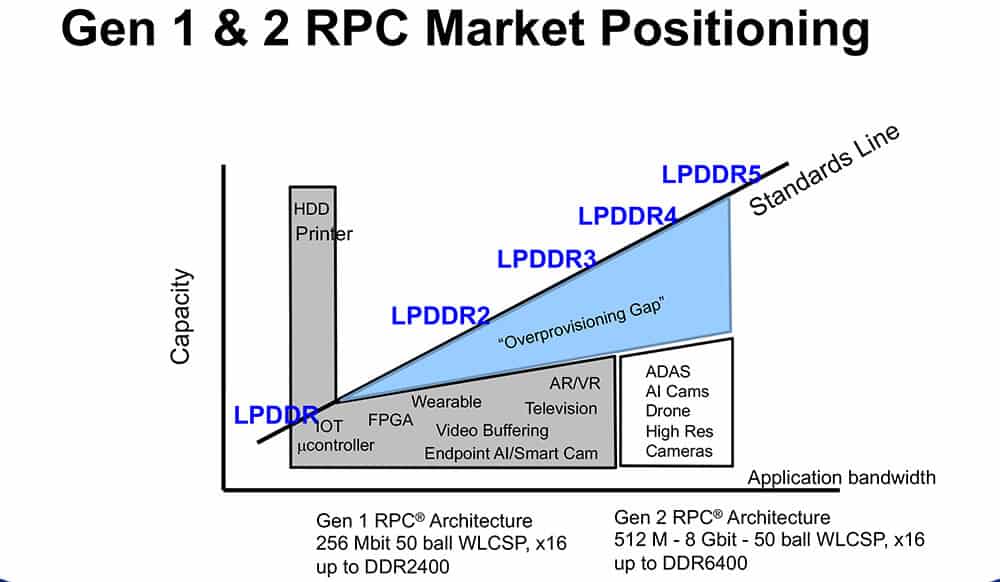

The Etron RPC DRAM® (RPC®) offers system users unique and valuable advantages. It adopts a wafer-level chip size package (WLCSP, a fan-in wafer-level die-scale package) that is the world's first high-bandwidth DRAM offered in a WLCSP. The x16 256 megabit RPC DRAM, has half the number of pins compared to similar bandwidth DDR3 products, and only needs 1/10 the PCB area. Thus, it can provide a path to both miniaturization and cost reduction. The RPC DRAM provides the same data bandwidth as a x16 DDR3 – LPDDR3 and therefore is suitable for bandwidth intensive applications such as AV multimedia streaming, but with less than half the IO pin count (24 switching signals).

Etron’s RPC DRAM interfaces to popular FPGA products to create the world's smallest machine learning and artificial intelligence products for video applications based on discrete components. When FPGAs are combined with the miniaturized RPC DRAM along with standard surface mount PCB technology, systems with minimum Size, Weight, Power and Cost (SWAP-C) result. This lays a solid foundation for the deployment of small form factor AI subsystems in high-volume and size-constrained applications. Since RPC DRAMs use less than half the FPGA IO pins of equivalent bandwidth DDR3, the RPC can double memory bandwidth compared to DDR3 while using fewer pins.

RPC Memory Controller for Lattice Nexus Family

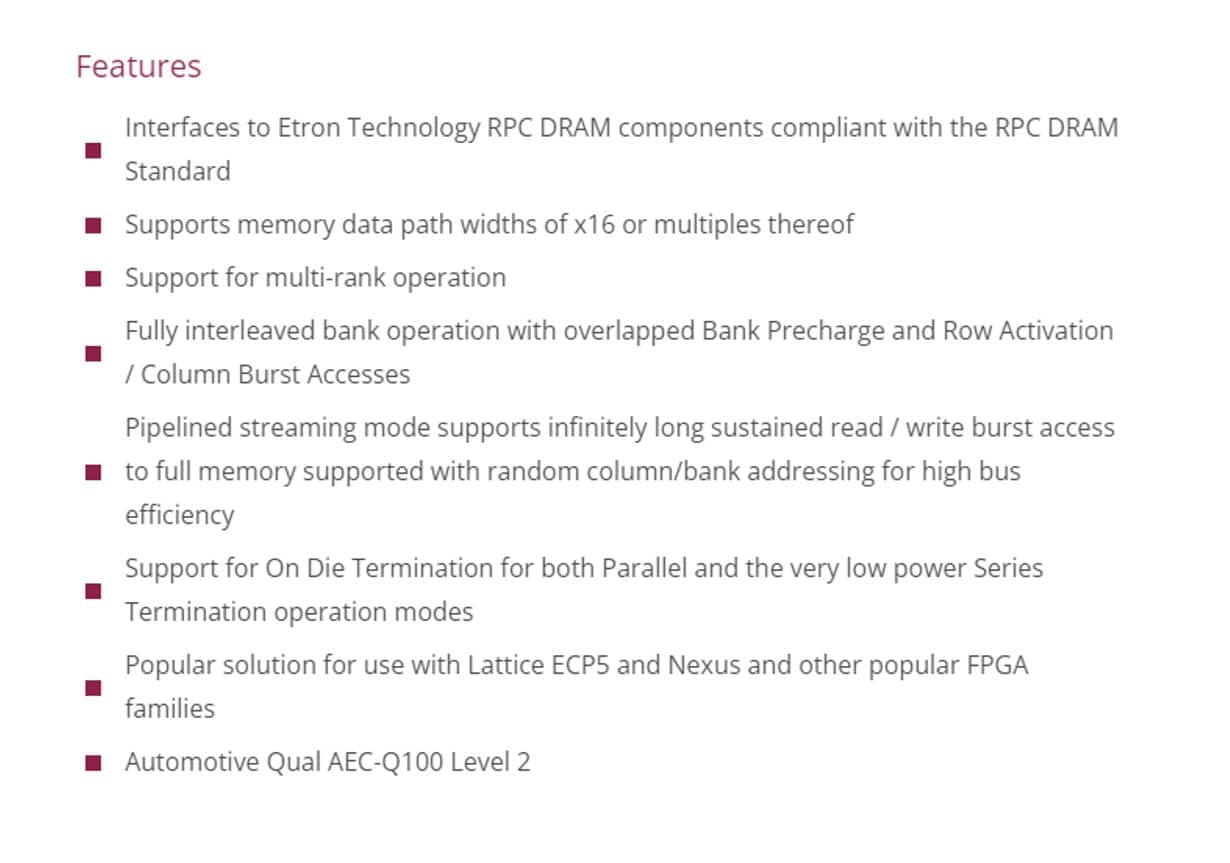

The RPC® Memory Controller IP by Citrobits is designed specifically for industrial applications. It is interfaced with the Etron Technology RPC DRAM Component, and uses Simplified User Interface which supports either 64- or 128-bit data width.

The design is implemented in Verilog HDL. The IP Core can be targeted to CertusPro™-NX FPGA devices. The IP Core is implemented using the Lattice Radiant™ software integrated with the Synplify Pro® synthesis tool.

Interface and Block Diagram

|

|