The Etron RPC DRAM (RPC) Dynamic Random Access Memory (DRAM) Controller is a general-purpose memory controller that interfaces the Lattice ECP5 family of FPGAs with Etron Technology’s Low Pincount RPC memory devices, and provides a generic command interface to user applications. The RPC DRAM is a high bandwidth x16-organized DDR-type DRAM, suitable for high bandwidth applications including high resolution video buffering, but featuring low pincount (24 switching IOs): using approximately half of the interface pins of DDR3/LPDDR3 yet offering the same bandwidth with similar high bus efficiency.

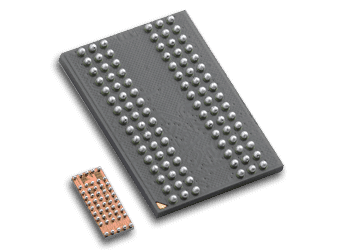

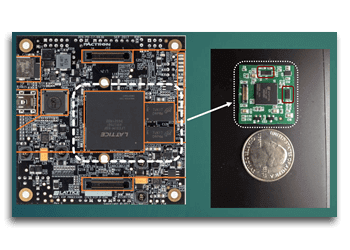

A unique and valuable advantage the RPC DRAM offers the system user is a Wafer Level CSP package option. The x16 RPC WLCSP occupies less than 10% of the PCB area of a standard x16 type DDR3 DRAM. It is the smallest possible discrete package and the first DRAM offered in this type of package. When paired with the miniaturized package options for the Lattice ECP5 family, an unprecedented level of cost-effective system miniaturization is enabled while using a standard surface mount PCB technology platform. For example, the PCB footprint area of the 285 csfBGA-packaged ECP5 combined with the WLCSP-packaged RPC DRAM is less than the area of a single x16 DDR3 DRAM.

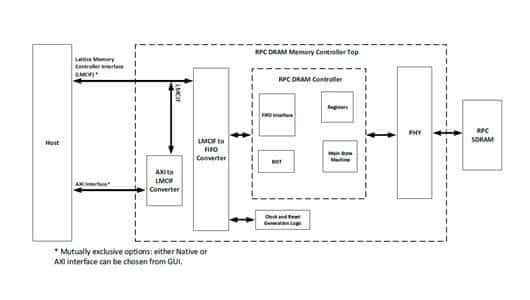

This core reduces the effort required to integrate RPC DRAM interfacing and control with the remainder of the application and eliminates the need for the application to directly deal with the RPC memory interface.