The Abu Dhabi AI Summit-Symbiotic Growth between Semiconductor and AI Industries for Booming IntelligenceN Economy

-

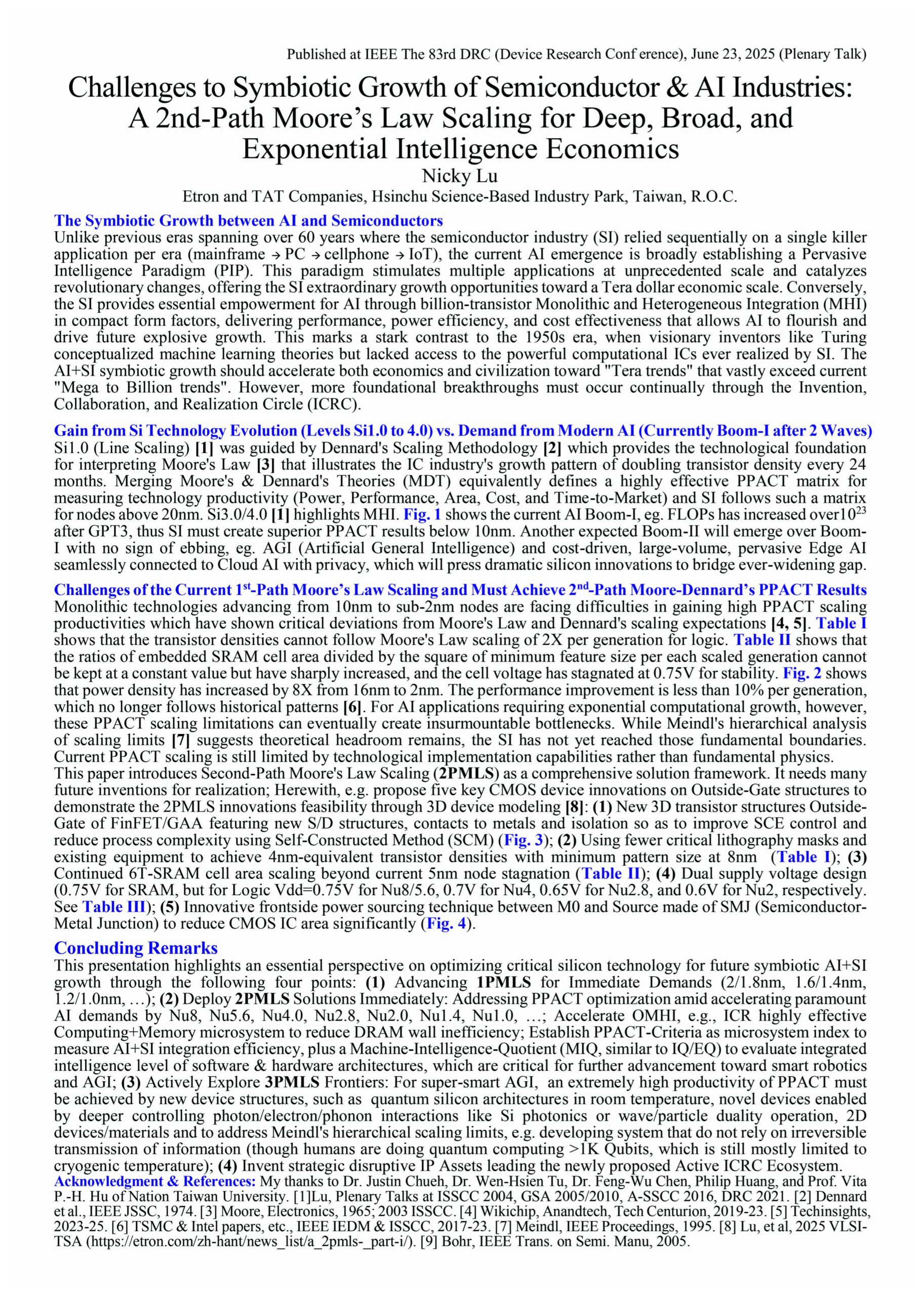

Symbiotic Growth of AI and Semiconductors: The presentation emphasizes the mutual reinforcement between AI and semiconductor industries, driving a booming “IntelligenceN” economy through innovations in Silicon 4.0 and Heterogeneous Integration (HI).

-

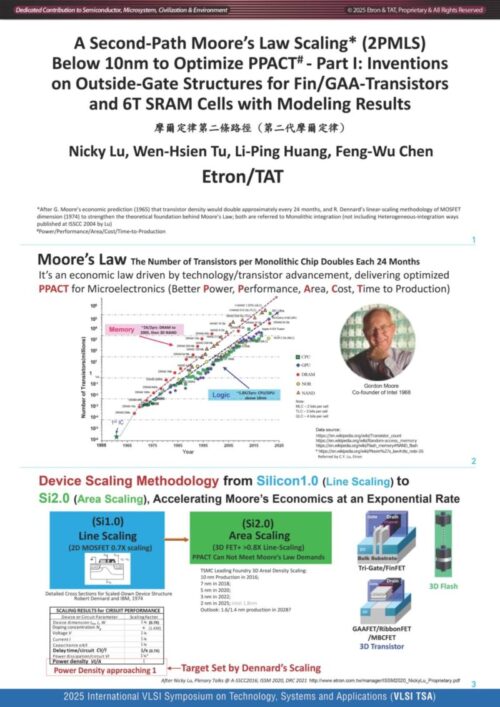

Evolution of Moore’s Law and OMHI: It introduces a “2nd Path” for Moore’s Law, focusing on Optimized Monolithic & Heterogeneous Integration (OMHI) to overcome physical scaling limits and address memory wall and energy challenges.

-

Emergence of Self-Smart Microsystems: The future points toward “Self-Smart Microsystems” that integrate logic, memory (DRAM), and AI hardware/software to enable diverse applications ranging from edge AI to bio-medical logic gates.

“MemorAiLink® Show Up” at CES 2026:Etron Tech Advances Edge AI and Robotics through On-Device Innovation

- RPC® inside G120 Subsystem – Honored with the “2025 Hsinchu Science Park Innovative Product Award.”

- New Scalable DDR3 Products and ASIC AI Memory – Developed through the MemorAiLink®

- EJ732 Series Chips – Successfully obtained the USB-IF USB PD3.2 DRP Controller Certification.

- Launch of Robotics Barebone Platforms – Introducing the AMR01C and AMR01M

- XINK Nano Platform –Successfully deployed in smart parking applications by Taiwan’s leading EV charging system integrator.

- Strategic Partnership with Asia Optical – Collaborating to create domestic delivery and robotic base barebone systems.

- Privacy-First AI Robot Decision System – Winner of the CES Innovation Award.

- “DecloakVision” – Recognized with the 22nd National Innovation Award.

【會員專屬 登入查閱全文】

ESWEEK 2025 – Embedded System Week – Dr Nicky Lu’s Slide Deck

Challenges in the Symbiosis between Semiconductors and AI: Optimizing Cost-Performance-Power through Second-Path Moore’s Law Scaling, Especially for Edge-AI Embedded Systems

【會員專屬 登入查閱全文】

A Second-Path Moore’s Law Scaling (2PMLS) Below 10nm to Optimize PPACT- Part I: Inventions on Outside-Gate Structures for Fin/GAA-Transistors and 6T SRAM Cells with Modeling Results

《A Second-Path Moore’s Law Scaling (2PMLS) Below 10nm to Optimize PPACT – Part I》。本篇聚焦於10奈米以下節點的創新途徑,深入探討FinFET與GAA晶體管結構的外閘技術(Outside-Gate Structures),以及6T SRAM單元的設計優化。

【會員專屬 登入查閱全文】

Challenges to Symbiotic Growth of Semiconductor & AI Industries: A 2nd-Path Moore’s Law Scaling for Deep, Broad, and Exponential Intelligence Economics

DRC是一個透過動手設計、團隊合作與問題解決來促進創新的平台。它鼓勵跨部門協作與實作學習,推動具實質價值的研發成果。

同體異質整合加乘 (Monolithic and Heterogeneous Integration, MHI™)

- 將矽和非矽之材料與元件的同體異質整合最佳化

- 創造由奈米矽核心與AI技術支援的Self-Smart微系統

SUSTAINABILITY

企業永續

鈺創科技股份有限公司全體管理層認知到遵守責任商業聯盟(RBA)是一個負責任的企業應具備的基本條件及致力努力的方向,企業除營利之餘,也應該取之於社會、用之於社會,並發揮對利害關係人的影響,包括員工、客戶、供應商、股東、公眾和政府等利益相關者的期望。

NEWS

最新消息-

產品專區

2026 鈺創以 MemorAiLink 打造完整 AI 記憶體生態系 整合多元 DRAM 產品組合、穩健供應 DDR4/LPDDR4/4X 全面布局 AI 運算與異質整合記憶體需求

-

公司營運

鈺創科技公佈二0二六年二月份合併營收報告

-

技術文章

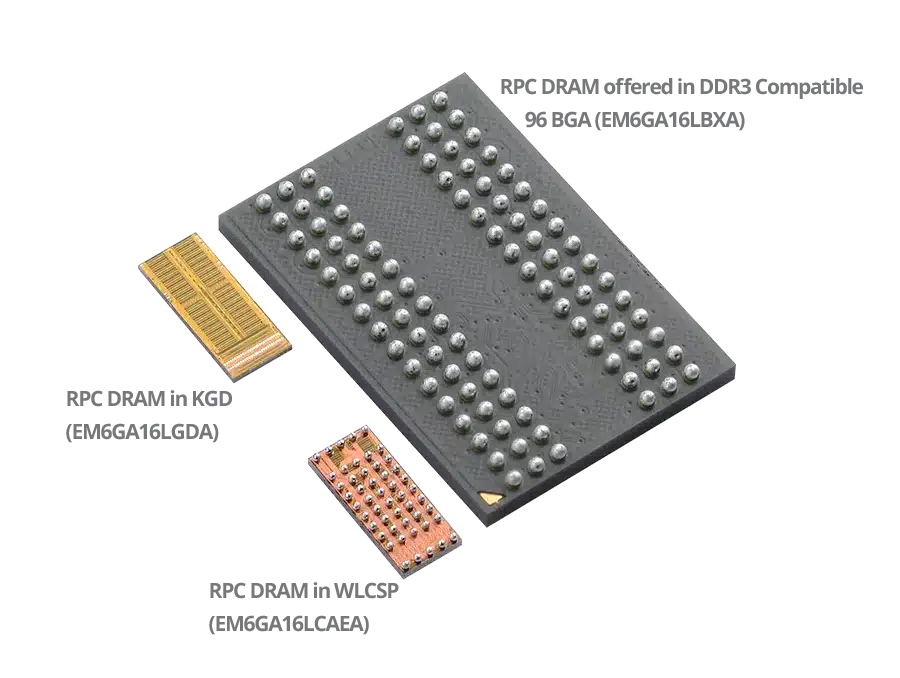

KGD 是什麼?認識KGD定義、功能與應用實例

-

影片活動

鈺創科技 RPC DRAM正式通過AEC-Q100 Grade-2車規級可靠度測試標準並成功進入國際領導品牌車廠的供應鏈 MemorAiLink記憶體IP平台在記憶體頻寬效能、次系統整體運算功耗及異質整合封裝技術的革新,有助於生成式AI擴展至邊緣端應用 高品質與高可靠度使鈺創成為 DRAM 產品長期穩定的供應商,支援AI 邊緣端應用逐步落地

RECRUIT

人才招募鈺創科技秉持培育菁英的理念,提供全方位培訓計畫與豐富的訓練資源,除積極規劃內部訓練,亦鼓勵同仁參與外部機構辦理之專業課程,用熱情成就夢想,築夢英雄們,竭誠歡迎您加入鈺創科技!

- 創新

- 榮譽

- 勇氣

- 團隊

COMPANY

關於鈺創於1991年2月成立於新竹科學園區,率先投入VLSI記憶體開發工作,承攬國家級「次微米計劃」設計工程, 開發 8 吋晶圓次微米技術,為台灣 DRAM、SRAM產業之蓬勃發展奠定深厚基礎。