RPC DRAM是一種新的DRAM架構,雖然市場對它並不熟悉,但它將展現能為終端視訊處理節點提供最佳整體SWaP-C的優勢。

在先前的「為即時視訊處理選擇SWaP-C最佳化方案」文章中,我們注意到運算處理正朝向邊緣(Edge),並將更進一步進入終端(Endpoint)。實作證明,透過採用分散式架構、即本地化的終端處理方案,比起以針對多媒體處理最佳化的現成商用邊緣處理器,能有機會進一步降低整體尺寸、重量、功率及成本(Size、Weight、Power與Cost,簡稱SWaP-C)。

若採用資源餘量(Headroom)多的選擇,剛開始的零件開銷可能會很便宜,但是最終可能會消耗更多的總功率,且在重量更大的情況下,會佔用更多的XYZ空間,且可能會產生熱源集中的散熱問題。進行SWaP-C分析將揭曉情況是否如此;記憶體是最可能被過度配置的元件之一,我們將展示它如何以多種方式加劇影響SWaP-C。我們也將討論可解決此一問題的新型DRAM。

RPC DRAM是一種256Mb元件,提供x16資料匯流排,可使用DDR介面之訊號運作。時脈頻率最高可達1200MHz (DDR2400),可使單一元件頻寬高達4800MB/秒。該DRAM由四個儲存記憶庫(four-bank)所組成,並可像標準DDR/LPDDR DRAM一樣,執行重疊的行和列運作。

如果使用資料位元組(8-bit)的資料選通(data strobes)訊號,則RPC DRAM具有24個切換訊號接口;如果選用16-bit的data strobes訊號模式,則RPC DRAM具有22-接腳介面。

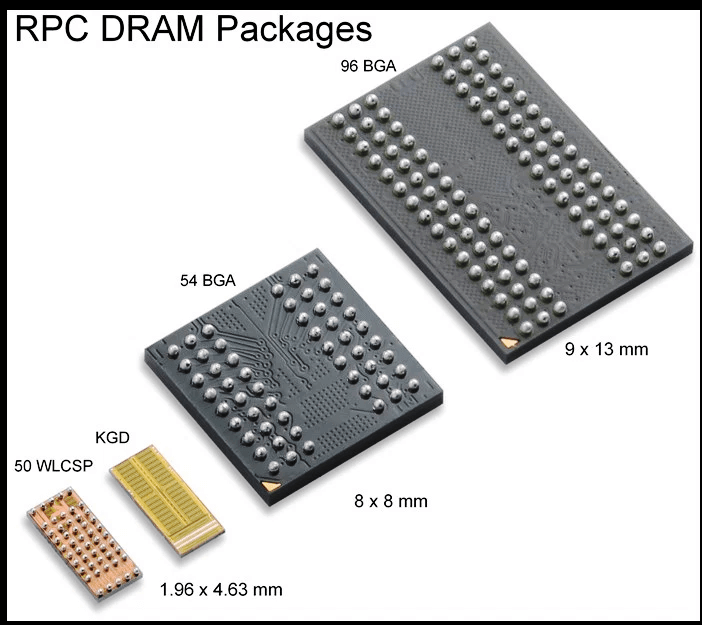

RPC DRAM選用的封裝型式如下圖。右邊是標準的96接腳BGA封裝,體積大約9 x 13 mm BGA,與用於x16規格之DDR3/DDR4 DRAM一樣的封裝;在某些系統中,該封裝中的RPC DRAM可與DDR3互換。最左邊是50接腳的1.96 x 2.63mm晶圓級晶粒尺寸封裝(WLCSP),這是第一個採用這種封裝的DRAM。緊接在旁的裸晶(KGD)型,通常用於裸晶堆疊之多晶片封裝(MCP)中。

RPC DRAM封裝。

值得一提的是,因為接腳數少,所有的接腳焊盤集中於裸晶長方形短邊(底部)邊緣。而旁邊的是小型54接腳BGA,尺寸是8×8 mm。它結合了縮小封裝尺寸及DDR3/DDR4 DRAM封裝於0.8mm接腳間距封裝技術,從而降低PCB製造之成本。

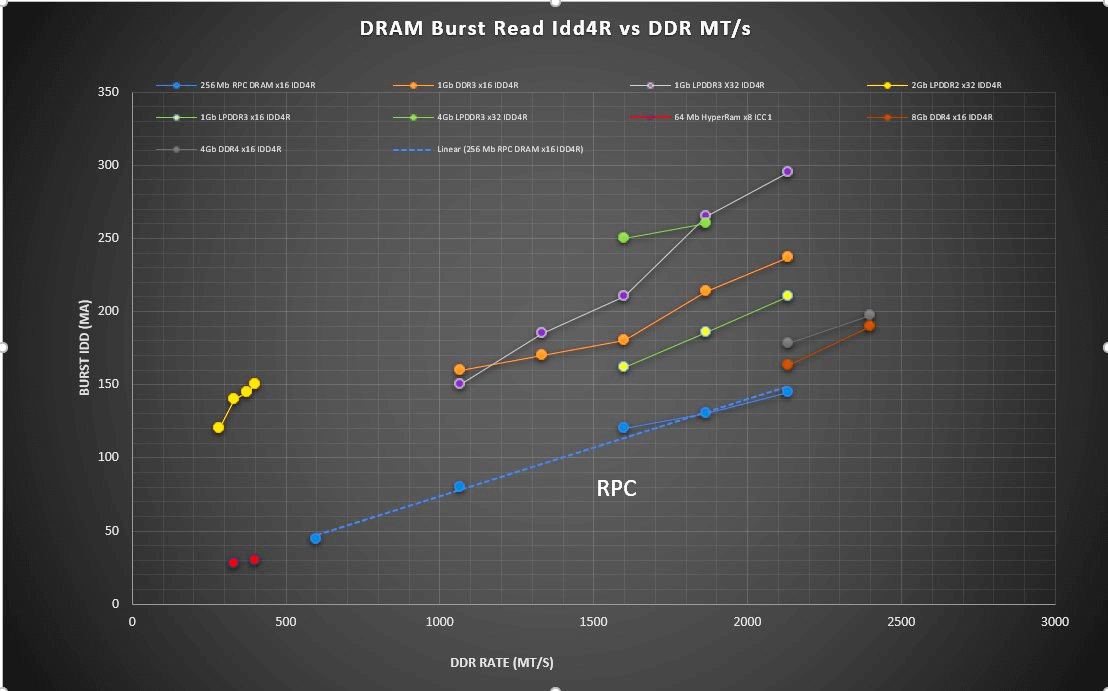

就功耗而言,與使用x16 DDR3/DDR4或x16 / x32 LPDDR3/LPDDR2或其它類似頻寬的記憶體次系統相比,RPC DRAM使用的運作電流最少。

不巧的是,這些DDR/LPDDR類型的記憶體通常無法提供低於1Gb的容量,而某些記憶體(如DDR4)容量從最小的4Gbit起跳。因此,僅根據頻寬而選擇的DDR3,LPDDR3或DDR4解決方案通常意味著為提供實際工作所需的bits數要多得多,這將會徒增許多不必要的功耗。

舉例而言,用於4K60影像之基準影格緩衝(frame buffer)設計通常需要大約200Mbit,並且需要在DDR667和DDR1600之間運作的x16匯流排的頻寬。通常需使用1、2或4Gbit DDR/LPDDR類型的DRAM:雖然會浪費能源或晶片佔位面積,但這是截至目前為止最好的選擇之一。

相較之下,RPC DRAM的容量和頻寬非常適合做為影像緩衝應用:容量為256 Mbit,其x16 DDR型介面,運作速度高達DDR2400 (MT/s)。使用WLCSP,與大容量DRAM相比,PCB所佔面積更小,且所需電流是選擇方案中最少的。

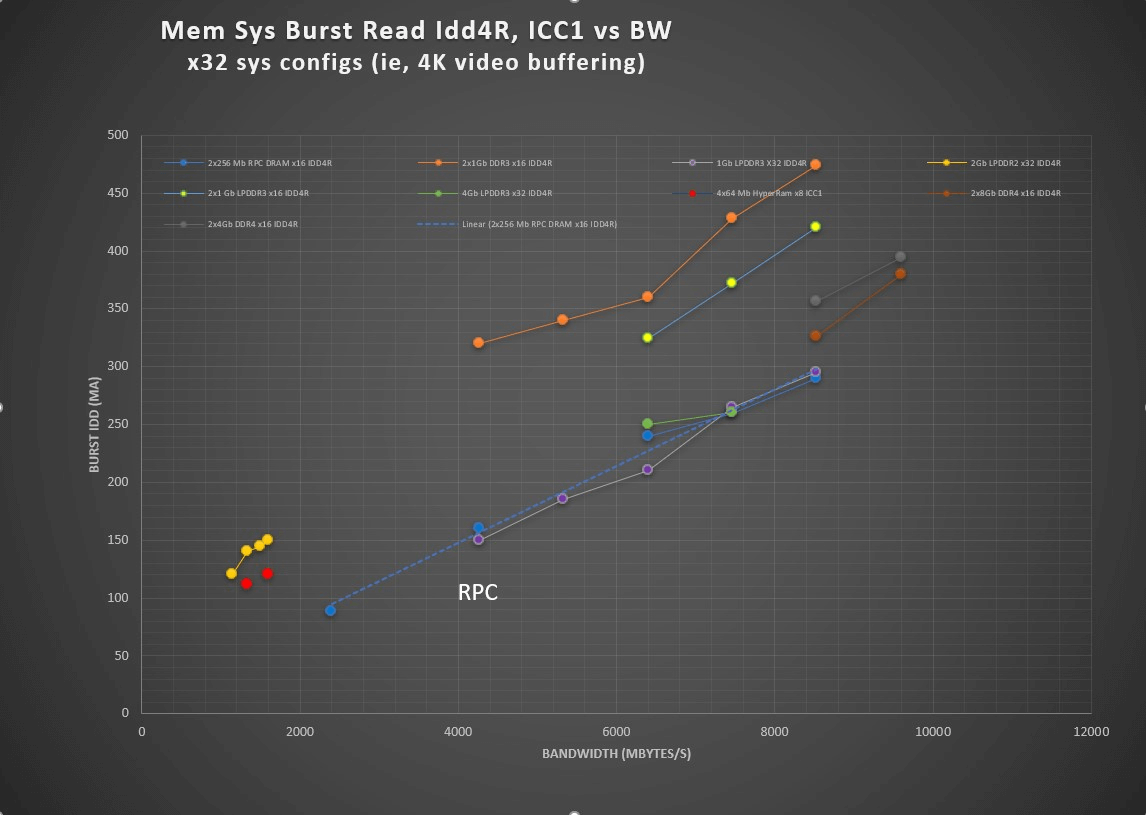

使用RPC DRAM進行影像緩衝意味著在影格緩衝RAM中浪費掉的位元數更少,進而減少功耗,並且在主動數據傳輸過程中切換的訊號數更少。如下圖所示,兩者均可以顯著地節省功率。

DRAM突發讀取電流與DRAM接腳速度的關聯。

根據位元數和頻寬來考量4K/60節點的記憶體選擇。對於16位元彩色深度大約需要133 Mbit,並且在影像輸入訊框(例如傳遞訊息180 f/s)時間內兩個完全寫入及讀取一個完整的影像訊框,大概需要一個16位元介面操作於DDR1550 MT/s。

某些FPGA無法運作於DDR3型記憶體等級的時脈頻率。因此,全速運作時必須使用大約兩倍的數據頻寬來補償操作頻率的不足。為此,導入16-bit及32-bit大的DDR3 DRAM應重新被檢視。此案所考慮的JEDEC標準記憶體IC有:1 Gbit x16 DDR3、1 Gbit x32 LPDDR3、1 Gbit x16 LPDDR3、2 Gbit x32 LPDDR2、4 Gbit x32 LPDDR3、4 Gbit x16 DDR4和8 Gbit x16 DDR4。

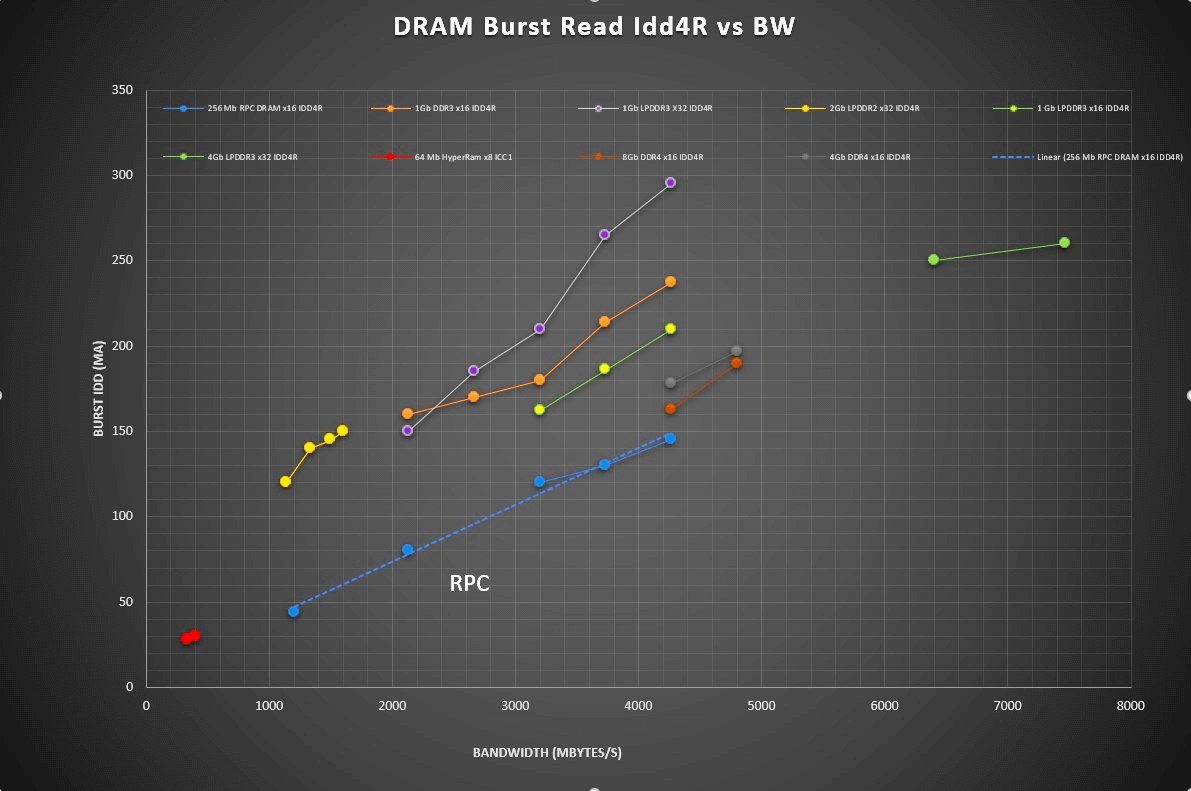

這些JEDEC標準型DRAM的某些元件處於其製造壽命的早期,而有些則接近尾聲。而所考慮的非標準型DRAM是256 Mbit x16 RPC DRAM和64 Mbit x8 HyperRAM。上圖是在突發讀取運作期間根據單個記憶體的工作電流之比較圖,較少的切換IO與較少的通電位元相結合,意味著RPC DRAM在給定的時脈頻率下使用最少的電流。要掌握更完整的樣貌,觀察單個記憶體的頻寬足可收效,如下圖所示。

DRAM突發讀取電流與單個DRAM頻寬的關係。

上圖比較了相同的DRAM,但繪製了突發工作電流與單個記憶體頻寬的關聯。這樣就可以取得DRAM匯流排寬度對系統頻寬的影響,進而評估需要大量頻寬的應用程序中使用的記憶體選擇方案,在相同的基礎上對x8、x16和x32記憶體組之DRAM進行比較。

下圖顯示了不同的系統對x32的輸出所需配置的工作電流。這些比較用於選擇為了滿足特定的視訊緩衝器頻寬和容量所需記憶體IC實體配置x32的總工作電流。為評估使用x32元件的設計,繪製了單個元件的突發讀取工作電流。 對於由x16元件製成的記憶體系統,則繪製了兩個此類元件的電流,而對於x8s,則繪製了四個此類元件的電流。

x32DRAM組突發讀取電流與系統頻寬之關聯。

顯然,無論如何比較這些低密度緩衝DRAM,RPC DRAM都為這些高頻寬但低容量的緩衝應用提供了適用配置中最低的工作電流解決方案。

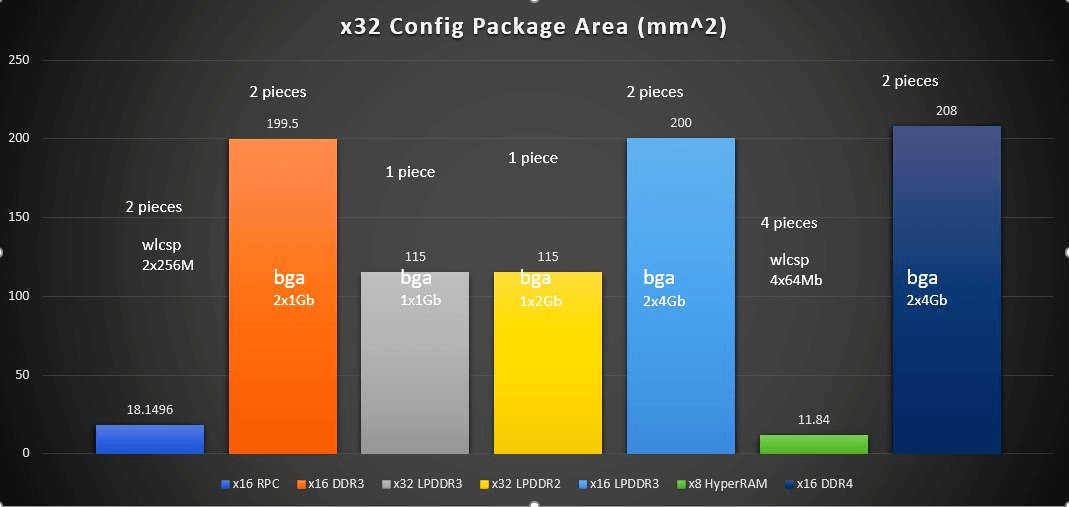

誠如前述,一個4K視訊緩衝區應用程序可能只需要200 megabits,而一些解決方案最終選擇4 Gigabit設備的原因是頻寬和市場上可取得的產品,卻不是以容量需求為考量,以致於相關的功率、面積倍增,突增不必要的成本。如圖所示,過度配置可能會導致成本高昂,而不是只看見的記憶體晶片成本。

RPC DRAM晶片不用PLL或DLL電路,這意味著一旦時脈重新啟動並穩定下來,RPC DRAM可以接受暫停的時脈,並可以在五個時脈週期內正常運轉。 這樣可以根據應用程序的內存需求快速停止和重新啟動記憶體通道,而在SoC/ASIC/FPGA中進一步提供系統的節能機會。

功耗並不足以說明全貌;但小型化趨勢對許多系統應用日益重要。與其它所有的高頻寬產品LPDDR2/3,DDR3/4相比,RPC DRAM採用的WLCSP封裝,其具有明顯的小型化優勢。下圖顯示了上述假設的x32系統的記憶體次系統封裝所佔用的PCB面積。對於x16組DRAM,使用此二種DRAM來提供x32匯流排。同樣,對於x32 DRAM或x8 DRAM,分別使用一個DRAM或四個DRAM。

x32組DRAM次系統之不同封裝記憶體所佔PCB區域比較。

儘管HyperRAM使用的PCB面積最少,但其提供有限的400 MT/s數據速率,僅達RPC DRAM及DDR3/4解決方案之每個接腳所提供的1600 MT/s速率的四分之一;其低頻寬和低bits數嚴重限制了其在這些高頻寬緩衝應用中的用途。在x32組DRAM使用時,它不能滿足4K / 60-16b應用程序之最低頻寬要求。

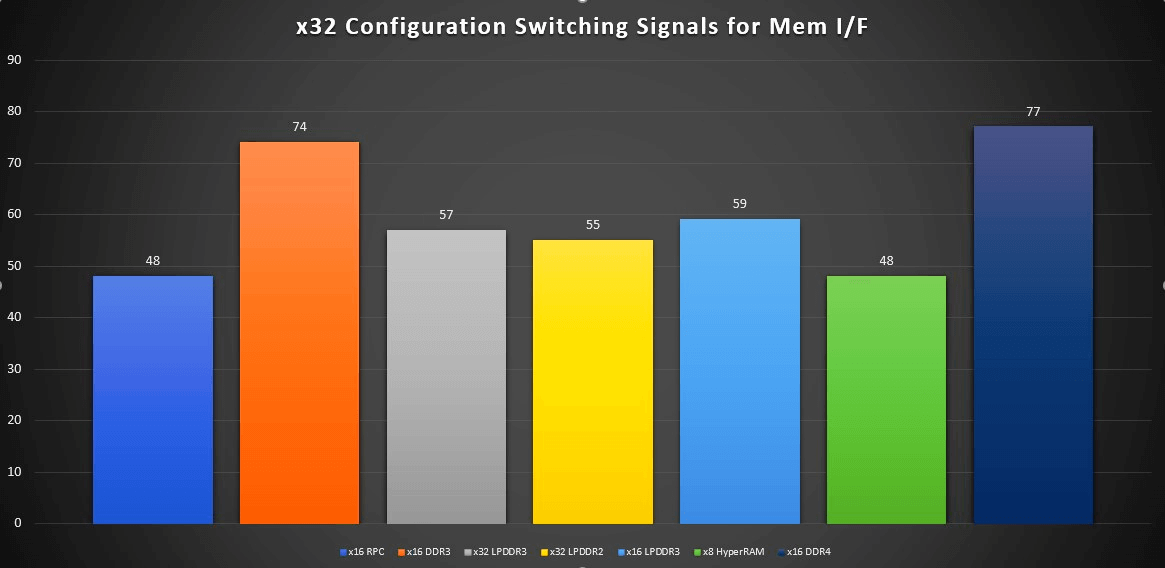

連接到外部記憶體次系統所需的接腳數是設計上的實體系統設計的考量之一。接腳數越多,用於控制記憶體的SOC/ASIC/FPGA上需要的接腳數就會愈多;而接腳愈多,意味著要更多的訊號佈線,這將導致需要更大面積的PCB:連接更多訊號會增加面積和PCB層數。再次強調,如上圖所示,RPC DRAM在各類高頻寬DRAM選擇方案中,屬接腳數最少。

x32組DRAM次系統之SOC/ASIC/FPGA記憶體介面的IO接腳數比較。

現有RPC DRAM提供WLCSP封裝、裸晶及兩種BGA型態(54或96接腳數)出貨。如本文前述,x16 RPC DRAM採用標準的96接腳x16 DDR3類型的封裝,並將數據匯流排、數據脈衝、時脈和電源接腳連接至個別對應之接腳,其餘未用到的接腳以N/C予以保留,這對於已採用DDR3 DRAM於FPGA系統應用中很流行,因為只要將DDR3 DRAM置換成同樣96接腳BGA封裝的RPC DRAM立即可以享受到使用RPC DRAM帶來種種的優點。

RPC DRAM旨在滿足對高頻寬但容量適中的記憶體系統需求,例如用於影像緩衝及其他頻寬密集型應用。當其與Lattice FPGA配對並部署在具有終端處理功能的分散式系統架構時,與標準DDR / LPDDR類型的DRAM相比,它不僅避免了記憶體系統容量的過度配置,更節省功率,減少PCB所佔面積和降低接腳數。

RPC DRAM和Lattice FPGA採用晶圓級WLCSP封裝,為半導體封裝提供最小體積且成本最低的IC產品,特別是與其他的小型化元件結合,創造出使用標準PCB製造技術卻能達成低成本次系統小型化之新境界。