RPC DRAM是一种新的DRAM架构,虽然市场对它并不熟悉,但它将展现能为终端视讯处理节点提供最佳整体SWaP-C的优势。

在先前的「为即时视讯处理选择SWaP-C最佳化方案」文章中,我们注意到运算处理正朝向边缘(Edge),并将更进一步进入终端(Endpoint)。实作证明,透过采用分布式架构、即本地化的终端处理方案,比起以针对多媒体处理最佳化的现成商用边缘处理器,能有机会进一步降低整体尺寸、重量、功率及成本(Size、Weight、Power与Cost,简称SWaP-C)。

若采用资源馀量(Headroom)多的选择,刚开始的零件开销可能会很便宜,但是最终可能会消耗更多的总功率,且在重量更大的情况下,会佔用更多的XYZ空间,且可能会产生热源集中的散热问题。进行SWaP-C分析将揭晓情况是否如此;记忆体是最可能被过度配置的元件之一,我们将展示它如何以多种方式加剧影响SWaP-C。我们也将讨论可解决此一问题的新型DRAM。

RPC DRAM是一种256Mb元件,提供x16资料汇流排,可使用DDR接口之讯号运作。时脉频率最高可达1200MHz (DDR2400),可使单一元件频宽高达4800MB/秒。该DRAM由四个储存记忆库(four-bank)所组成,并可像标准DDR/LPDDR DRAM一样,执行重叠的行和列运作。

如果使用资料位元组(8-bit)的资料选通(data strobes)讯号,则RPC DRAM具有24个切换讯号接口;如果选用16-bit的data strobes讯号模式,则RPC DRAM具有22-接脚接口。

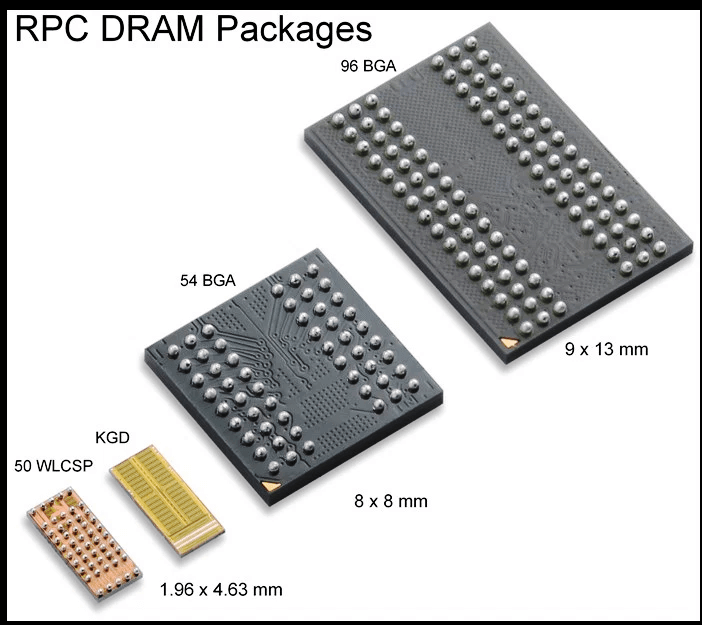

RPC DRAM选用的封装型式如下图。右边是标准的96接脚BGA封装,体积大约9 x 13 mm BGA,与用于x16规格之DDR3/DDR4 DRAM一样的封装;在某些系统中,该封装中的RPC DRAM可与DDR3互换。最左边是50接脚的1.96 x 2.63mm晶圆级晶粒尺寸封装(WLCSP),这是第一个采用这种封装的DRAM。紧接在旁的裸晶(KGD)型,通常用于裸晶堆叠之多芯片封装(MCP)中。

RPC DRAM封装。

值得一提的是,因为接脚数少,所有的接脚焊盘集中于裸晶长方形短边(底部)边缘。而旁边的是小型54接脚BGA,尺寸是8×8 mm。它结合了缩小封装尺寸及DDR3/DDR4 DRAM封装于0.8mm接脚间距封装技术,从而降低PCB制造之成本。

就功耗而言,与使用x16 DDR3/DDR4或x16 / x32 LPDDR3/LPDDR2或其它类似频宽的记忆体次系统相比,RPC DRAM使用的运作电流最少。

不巧的是,这些DDR/LPDDR类型的记忆体通常无法提供低于1Gb的容量,而某些记忆体(如DDR4)容量从最小的4Gbit起跳。因此,仅根据频宽而选择的DDR3,LPDDR3或DDR4解决方案通常意味着为提供实际工作所需的bits数要多得多,这将会徒增许多不必要的功耗。

举例而言,用于4K60影像之基准影格缓冲(frame buffer)设计通常需要大约200Mbit,并且需要在DDR667和DDR1600之间运作的x16汇流排的频宽。通常需使用1、2或4Gbit DDR/LPDDR类型的DRAM:虽然会浪费能源或芯片佔位面积,但这是截至目前为止最好的选择之一。

相较之下,RPC DRAM的容量和频宽非常适合做为影像缓冲应用:容量为256 Mbit,其x16 DDR型接口,运作速度高达DDR2400 (MT/s)。使用WLCSP,与大容量DRAM相比,PCB所佔面积更小,且所需电流是选择方案中最少的。

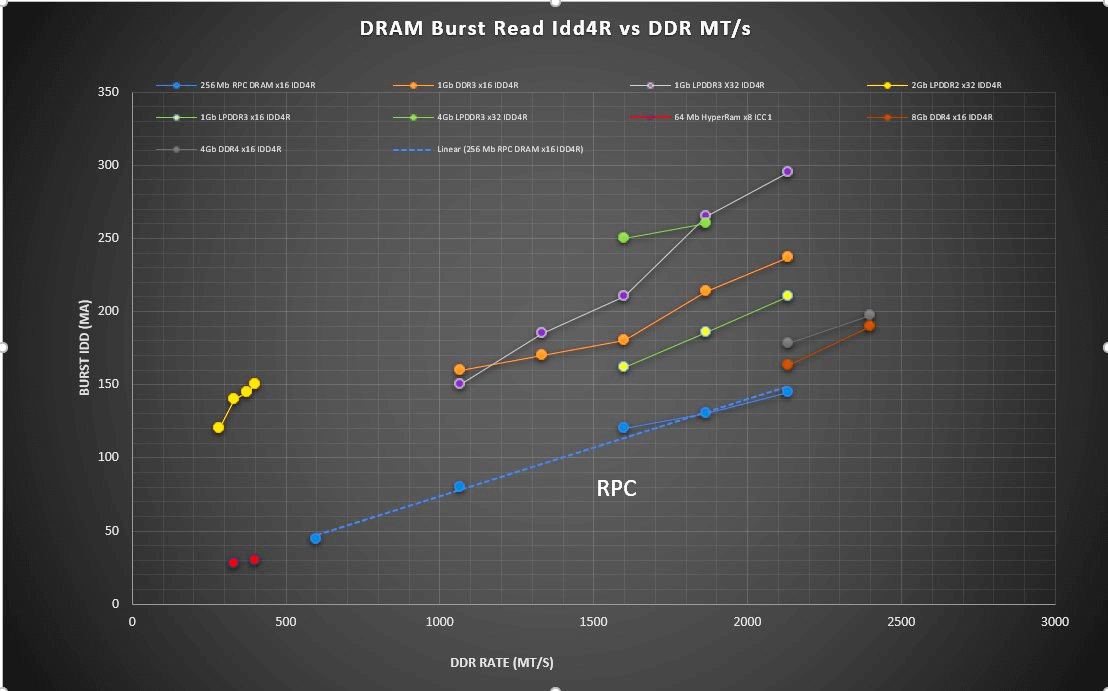

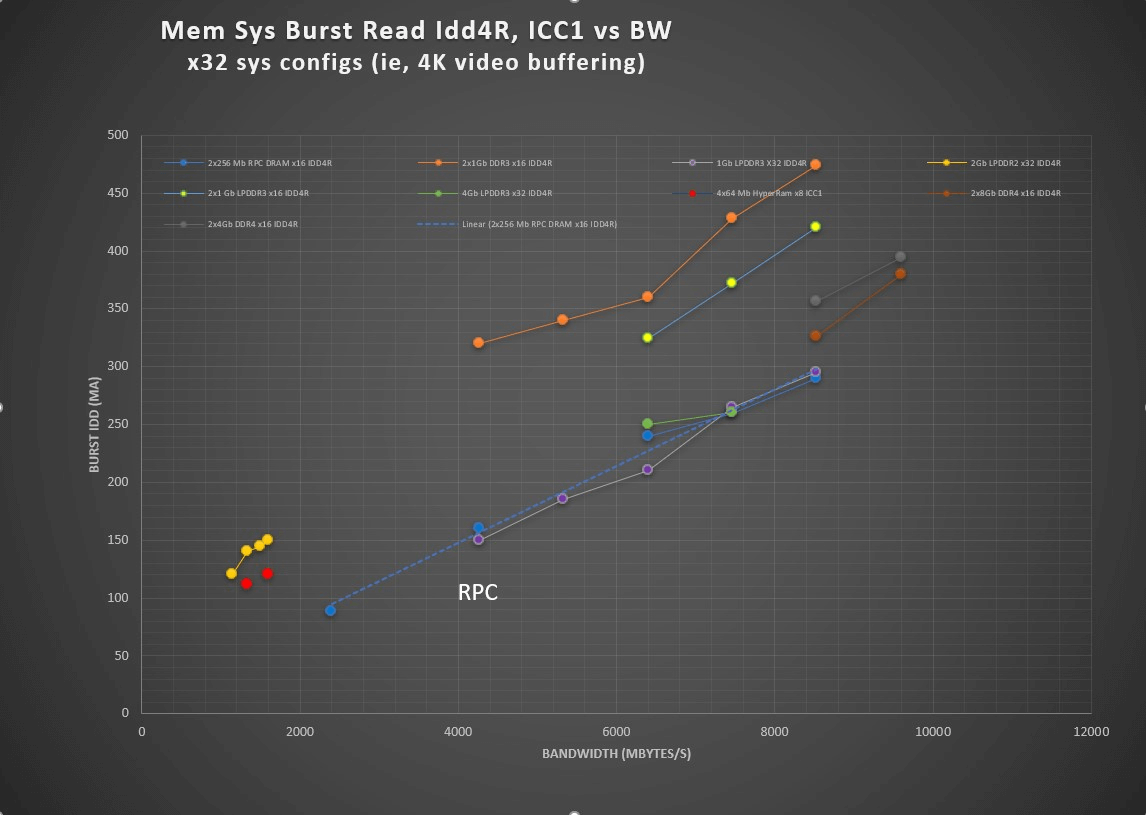

使用RPC DRAM进行影像缓冲意味着在影格缓冲RAM中浪费掉的位元数更少,进而减少功耗,并且在主动数据传输过程中切换的讯号数更少。如下图所示,两者均可以显着地节省功率。

DRAM突发读取电流与DRAM接脚速度的关联。

根据位元数和频宽来考量4K/60节点的记忆体选择。对于16位元彩色深度大约需要133 Mbit,并且在影像输入讯框(例如传递讯息180 f/s)时间内两个完全写入及读取一个完整的影像讯框,大概需要一个16位元接口操作于DDR1550 MT/s。

某些FPGA无法运作于DDR3型记忆体等级的时脉频率。因此,全速运作时必须使用大约两倍的数据频宽来补偿操作频率的不足。为此,导入16-bit及32-bit大的DDR3 DRAM应重新被检视。此案所考虑的JEDEC标准记忆体IC有:1 Gbit x16 DDR3、1 Gbit x32 LPDDR3、1 Gbit x16 LPDDR3、2 Gbit x32 LPDDR2、4 Gbit x32 LPDDR3、4 Gbit x16 DDR4和8 Gbit x16 DDR4。

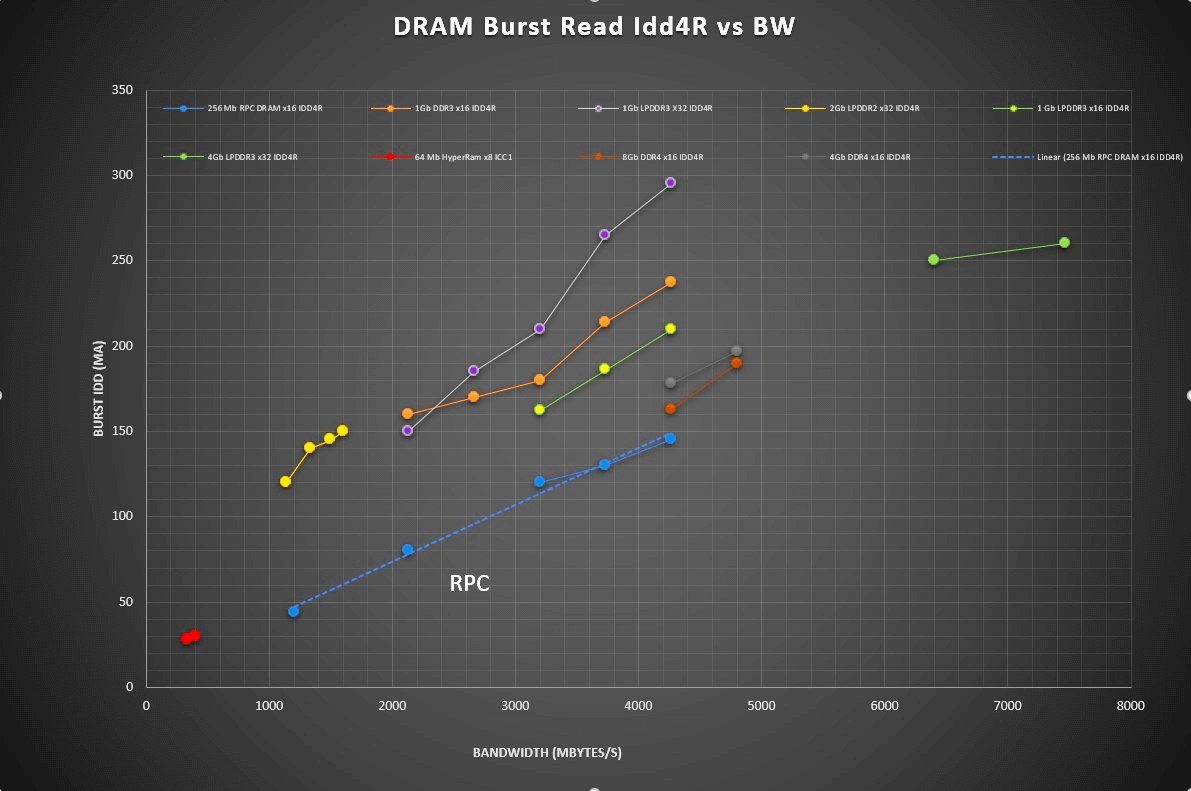

这些JEDEC标准型DRAM的某些元件处于其制造寿命的早期,而有些则接近尾声。而所考虑的非标准型DRAM是256 Mbit x16 RPC DRAM和64 Mbit x8 HyperRAM。上图是在突发读取运作期间根据单个记忆体的工作电流之比较图,较少的切换IO与较少的通电位元相结合,意味着RPC DRAM在给定的时脉频率下使用最少的电流。要掌握更完整的样貌,观察单个记忆体的频宽足可收效,如下图所示。

DRAM突发读取电流与单个DRAM频宽的关系。

上图比较了相同的DRAM,但绘制了突发工作电流与单个记忆体频宽的关联。这样就可以取得DRAM汇流排宽度对系统频宽的影响,进而评估需要大量频宽的应用程序中使用的记忆体选择方案,在相同的基础上对x8、x16和x32记忆体组之DRAM进行比较。

下图显示了不同的系统对x32的输出所需配置的工作电流。这些比较用于选择为了满足特定的视讯缓冲器频宽和容量所需记忆体IC实体配置x32的总工作电流。为评估使用x32元件的设计,绘制了单个元件的突发读取工作电流。 对于由x16元件制成的记忆体系统,则绘制了两个此类元件的电流,而对于x8s,则绘制了四个此类元件的电流。

x32DRAM组突发读取电流与系统频宽之关联。

显然,无论如何比较这些低密度缓冲DRAM,RPC DRAM都为这些高频宽但低容量的缓冲应用提供了适用配置中最低的工作电流解决方案。

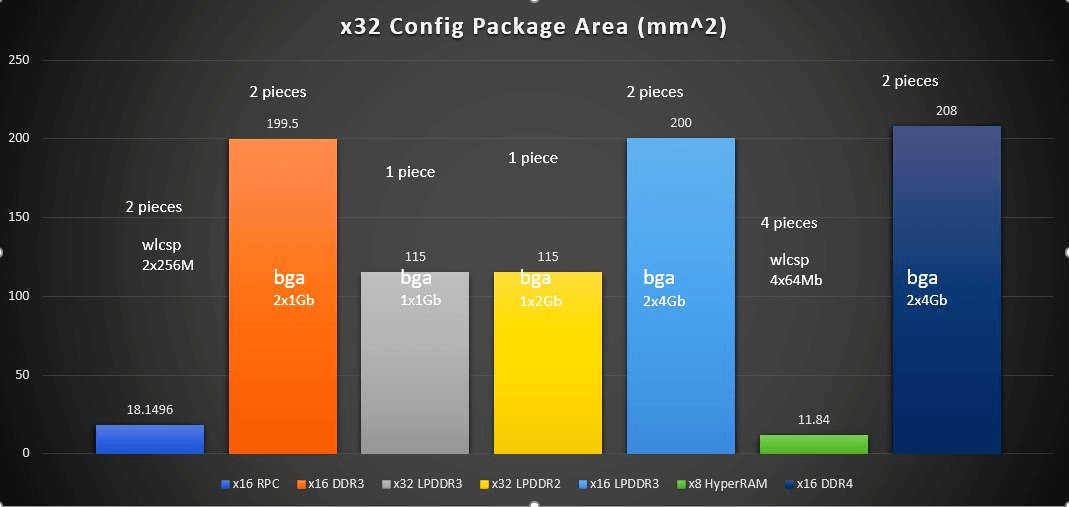

诚如前述,一个4K视讯缓冲区应用程序可能只需要200 megabits,而一些解决方案最终选择4 Gigabit设备的原因是频宽和市场上可取得的产品,却不是以容量需求为考量,以致于相关的功率、面积倍增,突增不必要的成本。如图所示,过度配置可能会导致成本高昂,而不是只看见的记忆体芯片成本。

RPC DRAM芯片不用PLL或DLL电路,这意味着一旦时脉重新启动并稳定下来,RPC DRAM可以接受暂停的时脉,并可以在五个时脉周期内正常运转。 这样可以根据应用程序的内存需求快速停止和重新启动记忆体信道,而在SoC/ASIC/FPGA中进一步提供系统的节能机会。

功耗并不足以说明全貌;但小型化趋势对许多系统应用日益重要。与其它所有的高频宽产品LPDDR2/3,DDR3/4相比,RPC DRAM采用的WLCSP封装,其具有明显的小型化优势。下图显示了上述假设的x32系统的记忆体次系统封装所佔用的PCB面积。对于x16组DRAM,使用此二种DRAM来提供x32汇流排。同样,对于x32 DRAM或x8 DRAM,分别使用一个DRAM或四个DRAM。

x32组DRAM次系统之不同封装记忆体所佔PCB区域比较。

尽管HyperRAM使用的PCB面积最少,但其提供有限的400 MT/s数据速率,仅达RPC DRAM及DDR3/4解决方案之每个接脚所提供的1600 MT/s速率的四分之一;其低频宽和低bits数严重限制了其在这些高频宽缓冲应用中的用途。在x32组DRAM使用时,它不能满足4K / 60-16b应用程序之最低频宽要求。

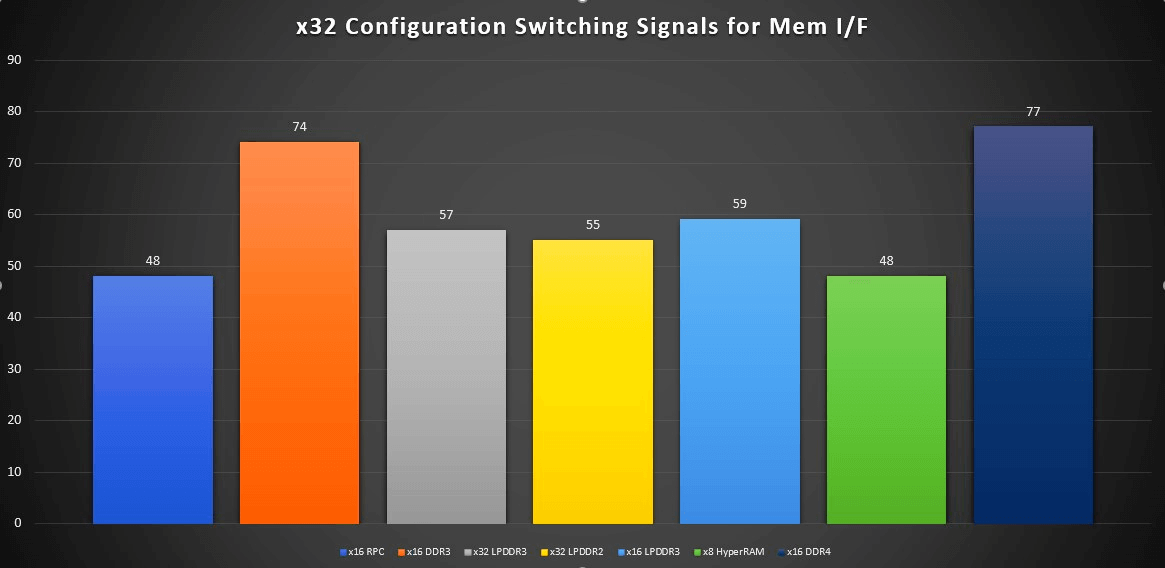

连接到外部记忆体次系统所需的接脚数是设计上的实体系统设计的考量之一。接脚数越多,用于控制记忆体的SOC/ASIC/FPGA上需要的接脚数就会愈多;而接脚愈多,意味着要更多的讯号布线,这将导致需要更大面积的PCB:连接更多讯号会增加面积和PCB层数。再次强调,如上图所示,RPC DRAM在各类高频宽DRAM选择方案中,属接脚数最少。

x32组DRAM次系统之SOC/ASIC/FPGA记忆体接口的IO接脚数比较。

现有RPC DRAM提供WLCSP封装、裸晶及两种BGA型态(54或96接脚数)出货。如本文前述,x16 RPC DRAM采用标准的96接脚x16 DDR3类型的封装,并将数据汇流排、数据脉冲、时脉和电源接脚连接至个别对应之接脚,其馀未用到的接脚以N/C予以保留,这对于已采用DDR3 DRAM于FPGA系统应用中很流行,因为只要将DDR3 DRAM置换成同样96接脚BGA封装的RPC DRAM立即可以享受到使用RPC DRAM带来种种的优点。

RPC DRAM旨在满足对高频宽但容量适中的记忆体系统需求,例如用于影像缓冲及其他频宽密集型应用。当其与Lattice FPGA配对并部署在具有终端处理功能的分布式系统架构时,与标准DDR / LPDDR类型的DRAM相比,它不仅避免了记忆体系统容量的过度配置,更节省功率,减少PCB所佔面积和降低接脚数。

RPC DRAM和Lattice FPGA采用晶圆级WLCSP封装,为半导体封装提供最小体积且成本最低的IC产品,特别是与其他的小型化元件结合,创造出使用标准PCB制造技术却能达成低成本次系统小型化之新境界。