# **Embedded Multi-Media Card (e.MMC)**

Flash Storage Specification e.MMC 5.1 HS400

EM74H08HVAGB-H

## **Revision History**

| Rev  | Date         | Comments        |

|------|--------------|-----------------|

| 1.00 | May 05, 2025 | Initial release |

Etron Technology, Inc. reserves the right to change products or specification without notice.

## 4GB e.MMC 5.1

# **EtronTech**

## **Contents**

| 1 | Introduction                                       | 6  |

|---|----------------------------------------------------|----|

|   | 1.1 Product Features                               |    |

|   | 1.2 e.MMC Specific Feature                         | 7  |

| 2 | Ball Assignment                                    | 8  |

|   | 2.1 Package Configuration                          | 8  |

|   | 2.2 Pins and Signal Description                    | ç  |

|   | 2.3 Product Block Diagram                          | 10 |

| 3 | S/W Algorithm                                      | 11 |

|   | 3.1 Partition Management                           | 11 |

|   | 3.2 Enhanced Partition (Area)                      | 11 |

|   | 3.3 User Density                                   | 12 |

|   | 3.4 Typical Performance                            | 12 |

|   | 3.5 Power Consumption                              | 13 |

| 4 | e.MMC Features Overview                            | 14 |

|   | 4.1 HS400 Interface                                | 15 |

|   | 4.2 Field Firmware Upgrade (FFU)                   | 15 |

|   | 4.3 Cache                                          | 15 |

|   | 4.4 Discard                                        | 15 |

|   | 4.5 Power off Notification                         | 15 |

|   | 4.6 Packed Commands                                | 16 |

|   | 4.7 Sleep (CMD5)                                   | 16 |

|   | 4.8 Enhanced Reliable Write                        | 16 |

|   | 4.9 Sanitize                                       | 16 |

|   | 4.10 Secure Erase                                  | 17 |

|   | 4.11 Secure Trim                                   | 17 |

|   | 4.12 High Priority Interrupt (HPI)                 | 17 |

|   | 4.13 H/W Reset                                     | 17 |

|   | 4.14 Command Queue                                 | 17 |

| 5 | Register Settings                                  | 18 |

|   | 5.1 OCR Register                                   | 18 |

|   | 5.2 Card Identification Register (CID)             |    |

|   | 5.3 Card Specific Data Register [CSD]              |    |

|   | 5.4 Extended Card Specific Data Register [EXT_CSD] | 21 |

| 6 | Electrical Characteristics                         | 25 |

|   | 6.1 Supply Voltage                                 | 25 |

|   | 6.2 Bus Signal Levels                              | 26 |

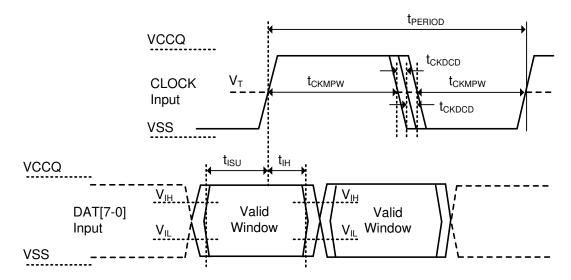

|   | 6.3 Bus Timing                                     |    |

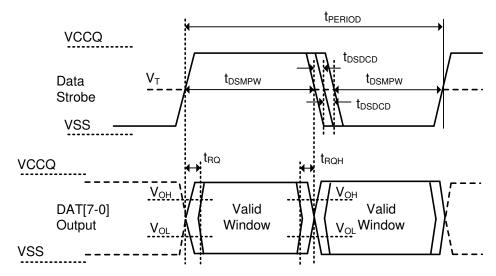

|   | 6.4 Bus Timing in HS400 mode                       | 29 |

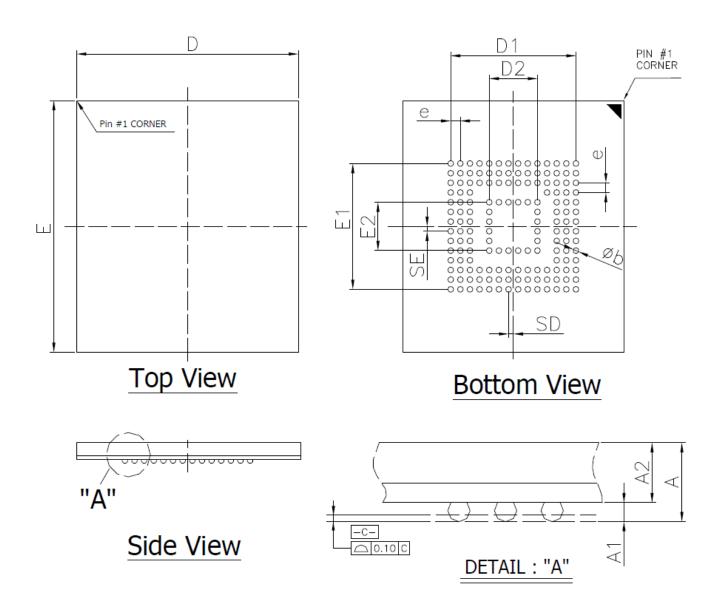

| 7 | Package Outline Information                        | 32 |

## 4GB e.MMC 5.1

# **EtronTech**

# **List of Figures**

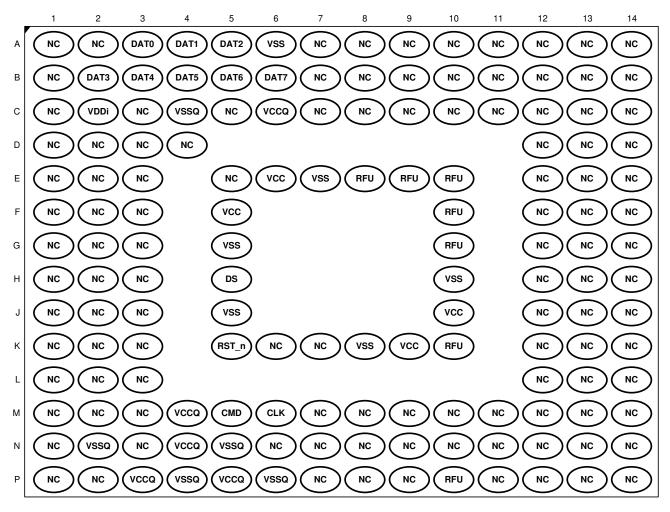

| Figure 2-1. 153-FBGA Ball Assignment (Top View) | 8  |

|-------------------------------------------------|----|

| Figure 2-2. e.MMC Block Diagram                 | 10 |

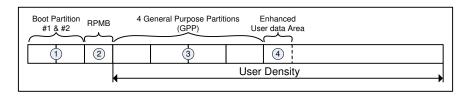

| Figure 3-1. Space Allocation in e.MMC           | 12 |

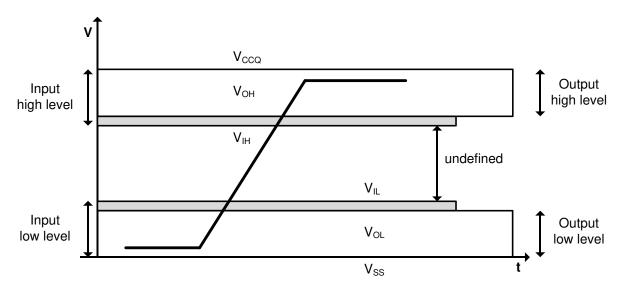

| Figure 6-1. Bus Signal Levels                   | 26 |

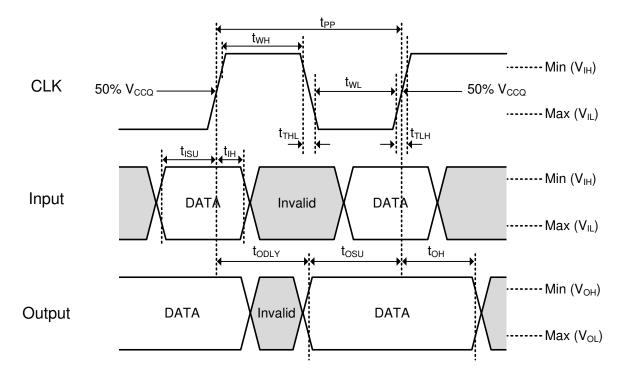

| Figure 6-2. Timing Diagram                      | 27 |

| Figure 6-3. HS400 Device Data input timing      | 29 |

| Figure 6-4. HS400 Device output timing          | 30 |

| Figure 7-1. Package Outline Drawing Information | 33 |

## 4GB e.MMC 5.1

# **EtronTech**

## **List of Tables**

| Table 1-1. Product Information                         | 6  |

|--------------------------------------------------------|----|

| Table 2-1. Communication Interface                     | 9  |

| Table 3-1. Capacity According to Partition             | 12 |

| Table 3-2. User Density and Enhanced Partition Size    | 12 |

| Table 3-3. Typical Performance                         | 12 |

| Table 3-4. Operating Current (RMS)                     | 13 |

| Table 3-5. Standby Power Consumption                   | 13 |

| Table 3-6. Sleep Power Consumption                     | 13 |

| Table 4-1. e.MMC Features Overview                     | 14 |

| Table 5-1. OCR Register Setting                        | 18 |

| Table 5-2. CID Register Setting                        | 19 |

| Table 5-3. CSD Register Setting                        | 20 |

| Table 5-4. Extended CSD Register Setting               | 21 |

| Table 6-1. Operating Voltage                           | 25 |

| Table 6-2. Bus Signal Level                            | 26 |

| Table 6-3. High-speed Device Interface Timing          | 27 |

| Table 6-4. Backward-compatible Device Interface Timing | 28 |

| Table 6-5. HS400 Device input timing                   | 29 |

| Table 6-6. HS400 Device output timing                  | 30 |

| Table 6-7. HS400 Capacitance                           | 31 |

| Table 7-1. FBGA (11.5 x 13.0 x 0.95mm) Dimension Table | 32 |

### 1 Introduction

The e.MMC products follow the JEDEC e.MMC 5.1 standards. It is an ideal universal storage solution for many electronic devices, including smart phones, tablets, PDAs, eBook readers, digital cameras, recorders, MP3, MP4 players, electronic learning products, digital TVs and set-top boxes. e.MMC encloses the MLC NAND and e.MMC controller inside as one JEDEC standard package, providing a standard interface to the host. The e.MMC controller directly manages NAND flash, including ECC, wear-leveling, IOPS optimization and read sensing.

#### 1.1 Product Features

- Packaged NAND flash memory with e.MMC 5.1 interface

- Backward compatible with all prior e.MMC specification revisions

- Operating Voltage Support:

- V<sub>CC</sub>: (3.3V) 2.7V ~ 3.6V

- $V_{CCQ}$ : (1.8V) 1.7V ~ 1.95V / (3.3V) 2.7V ~ 3.6V

- Temperature:

- Operating Temperature: TA = -25°C to +85°C

- Storage without operation: -40°C to +85°C

- Compliant with e.MMC 5.1 JEDEC Standard Number JESD84-B51

- Embedded Multi-Media storage in a single Multi-Chip package

- Package: 153-ball 11.5 x 13.0 x 0.95mm FBGA package

**Table 1-1. Product Information**

| Part Number    | NAND Density | V <sub>cc</sub> | V <sub>CCQ</sub> | Package |

|----------------|--------------|-----------------|------------------|---------|

| EM74H08HVAGB-H | 4 GB         | 3.3V            | 1.8V/3.3V        | FBGA    |

### 1.2 e.MMC Specific Feature

#### ■ JEDEC/e.MMC Standard version 5.1 Compatible (backward compatible to e.MMC 4.5)

- Supports a wide range of power supply voltage: 1.8 and 3.3V

- Supports HS400 Mode

- e.MMC production state awareness

- e.MMC device health report

- Supports Command Queue

- Programmable bus width: 1/4/8 bits

- Supports Boot operation in High Speed and DDR mode

- Supports Boot mode and Alternative Boot mode

- Replay Protection Memory Block (RPMB)

- Enhanced Partition Attributes

- High Priority Interrupt (HPI)

- Background operations

- Enhanced Reliable Write

- Secure removal types

- Enhance techniques: Sleep Notification in power off notification, data tagging, packed commands, discard, sanitize, RTC (real time clock)

#### ■ e.MMC Clock

- e.MMC I/F Clock Frequency : 0 ~ 200MHz

- e.MMC I/F Boot Frequency : 0 ~ 52MHz

#### ■ RoHS compliant

## 2 Ball Assignment

### 2.1 Package Configuration

Figure 2-1. 153-FBGA Ball Assignment (Top View)

## 2.2 Pins and Signal Description

The e.MMC device transfers data via a configurable number of data bus signals. The communication signals are:

**Table 2-1. Communication Interface**

| Name              | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CLK               | I                | Clock: Each cycle of this signal directs a one bit transfer on the command and either a one bit (1x) or a two bits transfer (2x) on all the data lines. The frequency may vary between zero and the maximum clock frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| DAT[7:0]          | I/O/PP           | <b>Data:</b> These are bidirectional data channels. The DAT signals operate in push-pull mode. Only the Device or the host is driving these signals at a time. By default, after power up or reset, only DAT0 is used for data transfer. A wider data bus can be configured for data transfer, using either DAT0-DAT3 or DAT0- DAT7, by the e.MMC host controller. The e.MMC device includes internal pull-ups for data lines DAT1-DAT7. Immediately after entering the 4-bit mode, the device disconnects the internal pull ups of lines DAT1, DAT2, and DAT3. Correspondingly, immediately after entering to the 8-bit mode, the device disconnects the internal pull-ups of lines DAT1-DAT7. |  |

| CMD               | I/O/PP/OD        | <b>Command:</b> This signal is a bidirectional command channel used for device initialization and transfer of commands. The CMD signal has two operation modes: open-drain for initialization mode, and push-pull for fast command transfer. Commands are sent from the e.MMC host controller to the e.MMC device and responses are sent from the device to the host.                                                                                                                                                                                                                                                                                                                           |  |

| RST_n             | I                | <b>Hardware Reset:</b> By default, hardware reset is disabled and must be enabled in the EXT_CSD register if used. Otherwise, it can be left un-connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| VCC               | S                | Supply voltage for core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| VCCQ              | S                | Supply voltage for I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| VSS               | S                | Supply ground for core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| VSSQ              | S                | Supply ground for I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| DS                | O/PP             | <b>Data Strobe:</b> This signal is generated by the device and used for output in HS400 mode. The frequency of this signal follows the frequency of CLK. For data output each cycle of this signal directs two bits transfer(2x) on the data - one bit for positive edge and the other bit for negative edge. For CRC status response output and CMD response output (enabled only HS400 enhanced strobe mode), the CRC status is latched on the positive edge only, and don't care on the negative edge.                                                                                                                                                                                       |  |

| RFU               | -                | Reserved for future use: These pins are not internally connected. Leave floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| NC                | -                | Not Connected: These pins are not internally connected. Signals can be routed through these balls to ease printed circuit board design.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| VDDi              | -                | Internal Voltage Node: Note that this is not a power supply input. This pin provides access to the output of an internal voltage regulator to allow for the connection of an external Creg capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| Note: I=Input; O= | Output; P=Push-F | Pull; OD=Open Drain; NC= No Connection and left floating; S=Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

### 2.3 Product Block Diagram

Figure 2-2. e.MMC Block Diagram

## 3 S/W Algorithm

### 3.1 Partition Management

e.MMC offers the possibility for the host to configure additional split local memory partitions with independent addressable space starting from logical address 0x00000000 for different usage models. Therefore memory block area can be classified as follows Factory configuration supplies two boot partitions implemented as enhanced storage media and one RPMB partitioning of 4MB in size.

Up to four General Purpose Area Partitions can be configured to store user data or sensitive data, or for other host usage models. The size of these partitions is a multiple of the write protect group.

### 3.2 Enhanced Partition (Area)

This e.MMC adopts Enhanced User Data Area as SLC Mode. Therefore when master adopts some portion as enhanced user data area in User Data Area, that area occupies triple size of original set up size. (For example, if master set 1MB for enhanced mode, total 3MB user data area is needed to generate 1MB enhanced area.)

### 3.3 User Density

Total User Density depends on device type. Different e.MMC part ID has different user density. The following diagram illustrates the memory space allocation within an e.MMC device.

Figure 3-1. Space Allocation in e.MMC

Table 3-1. Capacity According to Partition

| Capacity | Boot partition 1 | Boot partition 2 | RPMB    |

|----------|------------------|------------------|---------|

| 4GB      | 4096 KB          | 4096 KB          | 4096 KB |

Table 3-2. User Density and Enhanced Partition Size

| Capacity User Density Size |                    | Max. Enhanced Partition Size |  |

|----------------------------|--------------------|------------------------------|--|

| 4GB                        | 3,825,205,248 Byte | 1,912,602,624 Bytes          |  |

## 3.4 Typical Performance

The testing result is only for reference. Any change in testing environment may cause big difference in performance result.

**Table 3-3. Typical Performance**

| Capacity Read Sequential (MB/s) |           | Write Sequential (MB/s) |  |

|---------------------------------|-----------|-------------------------|--|

| 4GB                             | Up to 165 | Up to 55                |  |

### 3.5 Power Consumption

### 3.5.1 Operating Current (RMS)

**Table 3-4. Operating Current (RMS)**

| Capacity | Symbol | Read (mA) | Write (mA) |

|----------|--------|-----------|------------|

| 4GB      | ICC    | 29        | 20         |

|          | ICCQ   | 59        | 36         |

Note 1. The measurement for current is the average RMS current consumption over a period of 100ms.

### 3.5.2 Standby Power Consumption in auto power saving mode and standby state

**Table 3-5. Standby Power Consumption**

| Capacity | State   | ICC (uA) | ICCQ (uA) |

|----------|---------|----------|-----------|

| 4GB      | Standby | 31       | 71        |

Note 1. Power Measurement conditions: Bus configuration = x8, No CLK

Note 2. Typical value is measured at TA = 25  $^{\circ}$ C. Not 100% tested.

### 3.5.3 Sleep Power Consumption

**Table 3-6. Sleep Power Consumption**

| Capacity | State | ICC (uA) | ICCQ (uA) |

|----------|-------|----------|-----------|

| 4GB      | Sleep | 0        | 70        |

Note 1. Power Measurement conditions: Bus configuration = x8, No CLK

Note 2. Enter sleep state by CMD5, VCC power is switched off. Not 100% tested.

Note 2. Typical value is measured at TA = 25 °C.

## 4 e.MMC Features Overview

**Table 4-1. e.MMC Features Overview**

| e.MMC | Device Features              | Function                              | Support       |

|-------|------------------------------|---------------------------------------|---------------|

| NA    | INTERFACE                    | Speed                                 | HS400         |

| NA    | BUS SPEED                    | Max Speed                             | Up to 400MB/s |

| 4.41  | SECURE ERASE/TRIM            | "True Wipe"                           | YES           |

| 4.41  | BOOT AND MASS STORAGE        | One storage device (reduced BOM)      | YES           |

| 4.41  | PARTITION & PROTECTION       | Flexibility                           | YES           |

| 4.41  | BACKGROUND OPERATIONS        | Better user experience (low latency)  | YES           |

| 4.41  | POWER OFF NOTIFICATION       | Faster Boot; Responsiveness           | YES           |

| 4.41  | HARDWARE RESET               | Robust system design                  | YES           |

| 4.41  | HPI                          | Control long Reads/Writes             | YES           |

| 4.41  | RPMB                         | Secure folders                        | YES           |

| 4.5   | EXTENDED PARTITION ATTRIBUTE | Flexibility                           | YES           |

| 4.5   | LARGE SECTOR SIZE            | Potential performance                 | NO            |

| 4.5   | PACKED COMMANDS              | Reduce host overhead                  | YES           |

| 4.5   | DISCARD                      | Improved performance on full media    | YES           |

| 4.5   | DATA TAG                     | Performance and/or Reliability        | YES           |

| 4.5   | CONTEXT MANAGEMENT           | Performance and/or Reliability        | YES           |

| 4.5   | CACHE                        | Better sequential & random writes     | YES           |

| 4.51  | SANITIZE                     | "True Wipe"                           | YES           |

| 5.0   | FIELD FIRMWARE UPGRADE (FFU) | Enables feature enhancement           | YES           |

| 5.0   | PRODUCTION STATE AWARENESS   | Different operation during production | YES           |

| 5.0   | DEVICE HEALTH                | Vital NAND info                       | YES           |

| 5.1   | ENHANCE STROBE               | Sync Device and Host in HS400         | YES           |

| 5.1   | COMMAND QUEUE                | Responsiveness                        | YES           |

| 5.1   | RPMB THROUGHPUT              | Faster RPMB write throughput          | YES           |

| 5.1   | CACHE FLUSH AND BARRIER      | Order cache flushing                  | YES           |

| 5.1   | BKOPS CONTROLLER             | Host control on BLOPs                 | YES           |

| 5.1   | SECURE WP                    | Secure write protect                  | YES           |

| 5.1   | EUDA                         | Enhance User Data Area                | YES           |

#### 4.1 HS400 Interface

e.MMC supports HS400 signaling to achieve a bus speed of 400 MB/s via a 200MHz dual data rate clock frequency. HS400 mode supports 8 bits bus width and the 1.7 ~ 1.95 VCCQ option. Due to the speed, the host may need to have an adjustable sampling point to reliably receive the incoming data.

#### 4.2 Field Firmware Upgrade (FFU)

Field Firmware Updates (FFU) enables features enhancement in the field. Using this mechanism, the host downloads a new version of the firmware to the e.MMC device and instructs the e.MMC device to install the new downloaded firmware into the device. The entire FFU process occurs in the background without affecting the user/OS data. During the FFU process, the host can replace firmware files or single/all file systems.

#### 4.3 Cache

The e.MMC cache is dedicated volatile memory at the size of 512KB. Caching enables to improve e.MMC performance for both sequential and random access.

#### 4.4 Discard

e.MMC supports discard command as defined in e.MMC 5.1 spec. This command allows the host to identify data which is not needed, without requiring the device to remove the data from the Media. It is highly recommended for use to guarantee optimal performance of e.MMC and reduce amount of housekeeping operation.

#### 4.5 Power off Notification

e.MMC supports power off notifications as defined in e.MMC 5.1 spec. The usage of power off notifications allows the device to prepare itself to power off, and improve user experience during power-on. Note that the device may be set into sleep mode while power off notification is enabled.

Power off notification long allows the device to shutdown properly and save important data for fast boot time on the next power cycle.

#### 4.6 Packed Commands

To enable optimal system performance, e.MMC supports packed commands as defined in e.MMC 5.1 spec. It allows the host to pack Read or Write commands into groups (of single type of operation) and transfer these to the device in a single transfer on the bus. Thus, it allows reducing overall bus overheads.

### 4.7 Sleep (CMD5)

e.MMC may be switched between a Sleep and a Standby state using the SLEEP/AWAKE (CMD5). In the Sleep state the power consumption of the memory device is minimized and the memory device reacts only to the commands RESET (CMD0) and SLEEP/AWAKE (CMD5). All the other commands are ignored by the memory device. The VCC power supply may be switched off in Sleep state to enable even further system power consumption saving.

#### 4.8 Enhanced Reliable Write

e.MMC supports enhanced reliable write as defined in e.MMC 5.1 spec. Enhanced reliable write is a special write mode in which the old data pointed to by a logical address must remain unchanged until the new data written to same logical address has been successfully programmed. This is to ensure that the target address updated by the reliable write transaction never contains undefined data. When writing in reliable write, data will remain valid even if a sudden power loss occurs during programming.

#### 4.9 Sanitize

The Sanitize operation is used to remove data from the device. The use of the Sanitize operation requires the device to physically remove data from the unmapped user address space. The device will continue the sanitize operation, with busy asserted, until one of the following events occurs:

- Sanitize operation is complete

- HPI is used to abort the operation

- Power failure

- Hardware reset

After the sanitize operation is complete no data should exist in the unmapped host address space.

#### 4.10 Secure Erase

For backward compatibility reasons, in addition to the standard erase command the e.MMC supports the optional Secure Erase command.

This command allows the host to erase the provided range of LBAs and ensure no older copies of this data exist in the flash.

#### 4.11 Secure Trim

For backward compatibility reasons, e.MMC supports Secure Trim command. The Secure Trim command is similar to the Secure Erase command but performs a secure purge operation on write blocks instead of erase groups.

### 4.12 High Priority Interrupt (HPI)

The operating system usually uses demand-paging to launch a process requested by the user. If the host needs to fetch pages while in a middle of a write operation the request will be delayed until the completion of the write command.

The High Priority Interrupt (HPI), as defined in the e.MMC 5.1 specifications, allows for low-latency read operations by suspending a lower-priority task before its completion.

#### 4.13 H/W Reset

Hardware reset may be used by host to reset the device, moving the device to a Pre-idle state and disabling the power-on period write protect on blocks that were power-on write protected before the reset was asserted.

#### 4.14 Command Queue

e.MMC Command Queue enables device visibility of next commands and allows performance improvement. The protocol allows the host to queue up to 32 data-transfer commands in the device by implementing 5 new commands.

The benefits of command queuing are:

- Random Read performance improvement (higher IOPs)

- Reducing protocol overhead

- Command issuance allowed while data transfer is on-going

- · Device order the tasks according to best access to/from flash

## 5 Register Settings

Within the Device interface six registers are defined: OCR, CID, CSD, EXT\_CSD, RCA and DSR. These can be accessed only by corresponding commands. For more details, refer to the JEDEC Standard Specification JESD84-B51.

### 5.1 OCR Register

The 32-bit operation conditions register (OCR) stores the VDD voltage profile of the device and the access mode indication. In addition, this register includes a status information bit. This status bit is set if the device power up procedure has been finished. The OCR register shall be implemented by all devices.

**Table 5-1. OCR Register Setting**

| OCR Register Definitions OCR bit                     | VDD voltage window                 | High Voltage<br>Multi-Media Card     | Dual voltage<br>Multi-Media Card and e.MMC |  |  |

|------------------------------------------------------|------------------------------------|--------------------------------------|--------------------------------------------|--|--|

| [6:0]                                                | Reserved                           | 00 00000b                            | 00 00000b                                  |  |  |

| [7]                                                  | 1.70 - 1.95V                       | 0b                                   | 1b                                         |  |  |

| [14:8]                                               | 2.0 - 2.6V                         | 000 0000b                            | 000 0000b                                  |  |  |

| [23:15]                                              | 2.7 - 3.6V                         | 1 1111 1111b                         | 1 1111 1111b                               |  |  |

| [28:24]                                              | Reserved                           | 0 0000b                              | 0 0000b                                    |  |  |

| [30:29]                                              | Access Mode                        | 00b (byte mode)<br>10b (sector mode) | 00b (byte mode)<br>10b (sector mode)       |  |  |

| [31] (Device power up status bit (busy) <sup>1</sup> |                                    |                                      |                                            |  |  |

| Note1: This bit is set to LC                         | W if the Device has not finished t | he power up routine.                 |                                            |  |  |

## 5.2 Card Identification Register (CID)

The Card Identification (CID) register is 128 bits wide. It contains the Device identification information used during the device identification phase (e.MMC protocol). For more details, refer to the JEDEC Standard Specification JESD84-B51.

**Table 5-2. CID Register Setting**

| CID Fields Name       | Field | Width | CID slice | Value                  |

|-----------------------|-------|-------|-----------|------------------------|

| Manufacturer ID       | MID   | 8     | [127:120] | D5h                    |

| Reserved              | -     | 6     | [119:114] | 0h                     |

| Device/BGA            | CBX   | 2     | [113:112] | 01h                    |

| OEM/Application ID    | OID   | 8     | [111:104] | 18h                    |

| Product name          | PNM   | 48    | [103:56]  | (534237344848h) SB74HH |

| Product revision      | PRV   | 8     | [55:48]   | 01h                    |

| Product serial number | PSN   | 32    | [47:16]   | Random by Production   |

| Manufacturing date    | MDT   | 8     | [15:8]    | month, year            |

| CRC7 checksum         | CRC   | 7     | [7:1]     | CRC7 Generator         |

| not used, always "1"  | -     | 1     | [0]       | 1h                     |

## 5.3 Card Specific Data Register [CSD]

The Card-Specific Data (CSD) register provides information on how to access the contents stored in e.MMC. The CSD registers are used to define the error correction type, maximum data access time, data transfer speed, data format...etc. For more details, refer to the JEDEC Standard Specification JESD84-B51.

**Table 5-3. CSD Register Setting**

| Name                                             | Field              | Width | CSD-slice | Value          |

|--------------------------------------------------|--------------------|-------|-----------|----------------|

| CSD structure                                    | CSD_STRUCTURE      | 2     | [127:126] | 3h             |

| System specification version                     | SPEC_VERS          | 4     | [125:122] | 4h             |

| Reserved                                         | -                  | 2     | [121:120] | -              |

| Data read access-time 1                          | TAAC               | 8     | [119:112] | 27h            |

| Data read access-time 2 in CLK cycles (NSAC*100) | NSAC               | 8     | [111:104] | 01h            |

| Max. bus clock frequency                         | TRAN_SPEED         | 8     | [103:96]  | 32h            |

| Device command classes                           | ccc                | 12    | [95:84]   | 0F5h           |

| Max. read data block length                      | READ_BL_LEN        | 4     | [83:80]   | 9h             |

| Partial blocks for read allowed                  | READ_BL_PARTIAL    | 1     | [79:79]   | 0h             |

| Write block misalignment                         | WRITE_BLK_MISALIGN | 1     | [78:78]   | 0h             |

| Read block misalignment                          | READ_BLK_MISALIGN  | 1     | [77:77]   | 0h             |

| DSR implemented                                  | DSR_IMP            | 1     | [76:76]   | 0h             |

| Reserved                                         | -                  | 2     | [75:74]   | -              |

| Device size                                      | C_SIZE             | 12    | [73:62]   | FFFh           |

| Max. read current @ VDD min                      | VDD_R_CURR_MIN     | 3     | [61:59]   | 7h             |

| Max. read current @ VDD max                      | VDD_R_CURR_MAX     | 3     | [58:56]   | 7h             |

| Max. write current @ VDD min                     | VDD_W_CURR_MIN     | 3     | [55:53]   | 7h             |

| Max. write current @ VDD max                     | VDD_W_CURR_MAX     | 3     | [52:50]   | 7h             |

| Device size multiplier                           | C_SIZE_MULT        | 3     | [49:47]   | 7h             |

| Erase group size                                 | ERASE_GRP_SIZE     | 5     | [46:42]   | 1Fh            |

| Erase group size multiplier                      | ERASE_GRP_MULT     | 5     | [41:37]   | 1Fh            |

| Write protect group size                         | WP_GRP_SIZE        | 5     | [36:32]   | 0Fh            |

| Write protect group enable                       | WP_GRP_ENABLE      | 1     | [31:31]   | 1h             |

| Manufacturer default ECC                         | DEFAULT_ECC        | 2     | [30:29]   | 0h             |

| Write speed factor                               | R2W_FACTOR         | 3     | [28:26]   | 2h             |

| Max. write data block length                     | WRITE_BL_LEN       | 4     | [25:22]   | 9h             |

| Partial blocks for write allowed                 | WRITE_BL_PARTIAL   | 1     | [21:21]   | 0h             |

| Reserved                                         | -                  | 4     | [20:17]   | -              |

| Content protection application                   | CONTENT_PROT_APP   | 1     | [16:16]   | 0h             |

| File format group                                | FILE_FORMAT_GRP    | 1     | [15:15]   | 0h             |

| Copy flag (OTP)                                  | COPY               | 1     | [14:14]   | 0h             |

| Permanent write protection                       | PERM_WRITE_PROTECT | 1     | [13:13]   | 0h             |

| Temporary write protection                       | TMP_WRITE_PROTECT  | 1     | [12:12]   | 0h             |

| File format                                      | FILE_FORMAT        | 2     | [11:10]   | 0h             |

| ECC code                                         | ECC                | 2     | [9:8]     | 0h             |

| CRC                                              | CRC                | 7     | [7:1]     | CRC7 Generator |

| Not used, always'1'                              | -                  | 1     | [0:0]     | -              |

### 5.4 Extended Card Specific Data Register [EXT\_CSD]

The Extended CSD register defines the Device properties and selected modes. It is 512 bytes long. The most significant 320 bytes are the Properties segment, which defines the Device capabilities and cannot be modified by the host. The lower 192 bytes are the Modes segment, which defines the configuration the Device is working in. These modes can be changed by the host by means of the SWITCH command. For more details, refer to the JEDEC Standard Specification JESD84-B51.

Table 5-4. Extended CSD Register Setting

| Name                                       | Field                                         | Size (Bytes) | CSD-slice | Value            |

|--------------------------------------------|-----------------------------------------------|--------------|-----------|------------------|

| Properties Segment                         |                                               | , , ,        | · I       |                  |

| Reserved                                   | _                                             | 6            | [511:505] | -                |

| Supported Command Sets                     | S_CMD_SET                                     | 1            | [504]     | 1h               |

| HPI features                               | HPI_FEATURES                                  | 1            | [503]     | 1h               |

| Background operations support              | BKOPS SUPPORT                                 | 1            | [502]     | 1h               |

| Max packed read commands                   | MAX_PACKED_READS                              | 1            | [501]     | 20h              |

| Max packed write commands                  | MAX PACKED WRITES                             | 1            | [500]     | 20h              |

| Data Tag Support                           | DATA_TAG_SUPPORT                              | 1            | [499]     | 1h               |

| Tag Unit Size                              | TAG_UNIT_SIZE                                 | 1            | [498]     | 0h               |

| Tag Resources Size                         | TAG_RES_SIZE                                  | 1            | [497]     | 0h               |

| Context management capabilities            | CONTEXT_CAPABILITIES                          | 1            | [496]     | 78h              |

| Large Unit size                            | LARGE_UNIT_SIZE_M1                            | 1            | [495]     | 1h               |

| Extended partitions attribute support      | EXT_SUPPORT                                   | 1            | [494]     | 3h               |

| Supported modes                            | SUPPORTED_MODES                               | 1            | [493]     | 1h               |

| FFU features                               | FFU_FEATURES                                  | 1            | [492]     | 0h               |

| Operation codes timeout                    | OPERATION_CODE_TIME_OUT                       | 1            | [491]     | 17h              |

| FFU Argument                               | FFU_ARG                                       | 4            | [490:487] | FFFAFFF0h        |

| Barrier support                            | BARRIER_SUPPORT                               | 1            | [486:486] | 1h               |

| Reserved                                   | _                                             | 177          | [485:309] | -                |

| CMD Queuing Support                        | CMQ_SUPPORT                                   | 1            | [308:308] | 1h               |

| CMD Queuing Depth                          | CMQ_DEPTH                                     | 1            | [307:307] | 1Fh              |

| Reserved                                   | Reserved                                      | 1            | [306:306] | -                |

| Number of FW sectors correctly programmed  | NUMBER_OF_FW_SECTORS_<br>CORRECTLY_PROGRAMMED | 4            | [305:302] | 0h               |

| Vendor proprietary health report           | VENDOR_PROPRIETARY_<br>HEALTH_REPORT          | 32           | [301:270] | 0h               |

| Device life time estimation type B         | DEVICE_LIFE_TIME_EST_TYP_B                    | 1            | [269]     | 1h               |

| Device life time estimation type A         | DEVICE_LIFE_TIME_EST_TYP_A                    | 1            | [268]     | 1h               |

| Pre EOL information                        | PRE_EOL_INFO                                  | 1            | [267]     | 1h               |

| Optimal read size                          | OPTIMAL_READ_SIZE                             | 1            | [266]     | 40h              |

| Optimal write size                         | OPTIMAL_WRITE_SIZE                            | 1            | [265]     | 40h              |

| Optimal trim unit size                     | OPTIMAL_TRIM_UNIT_SIZE                        | 1            | [264]     | 7h               |

| Device version                             | DEVICE_VERSION                                | 2            | [263:262] | 3405h            |

| Firmware version                           | FIRMWARE_VERSION                              | 8            | [261:254] | 000000000000010h |

| Power class for 200MHz,<br>DDR at VCC=3.6V | PWR_CL_DDR_200_360                            | 1            | [253]     | 00h              |

| Cache size                                 | CACHE_SIZE                                    | 4            | [252:249] | 0400h            |

| Generic CMD6 timeout                       | GENERIC_CMD6_TIME                             | 1            | [248]     | 05h              |

| Power off notification(long) time out      | POWER_OFF_LONG_TIME                           | 1            | [247]     | 64h              |

| Sumber of correctly   Default = 0h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Background operations status       | BKOPS STATUS            | 1 | [246]     | Default = 0h  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------|---|-----------|---------------|

| Default of   Def   | -                                  | _                       | ' |           | Delault - 011 |

| Ist Initialization time after partitioning NII_TIMECUT_AP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ,                                  |                         | 4 | [245:242] | Default = 0h  |

| Cache Flushing Policy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                    |                         | 1 | [241]     | 0Ah           |

| Power class for S2MHz. DDR at 3.5V PWR. CL. DDR. 52.360   1   2331   0h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    |                         | 1 |           |               |

| Power class for S2MHz, DDR at 1,98V PWR CL_ DDR S2_195   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                    |                         | 1 |           |               |

| Power class for 200MHz, at 1.95V   PWR_CL_200_360   1   237]   236                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                    |                         | 1 | · -       |               |

| Power class for 200MHz, at 1.95V   PWR_CL_200_195   1   236                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                    |                         | 1 |           |               |

| Minimum Write Performance for 8bit at 52MHz in DDR mode   MIN_PERF_DDR_W_8_52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    |                         | 1 | · -       |               |

| Minimum Read Performance for 8bit at 52MHz in DDR mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Minimum Write Performance for 8bit |                         | 1 | f -       |               |

| TRIM Multiplier   TRIM_MULT   1   232  2h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Minimum Read Performance for 8bit  | MIN_PERF_DDR_R_8_52     | 1 | [234]     | 0h            |

| Secure Feature support   SEC_FEATURE SUPPORT   1   231   55h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reserved                           | _                       | 1 | [233]     | -             |

| Secure Feature support   SEC_FEATURE_SUPPORT   1   231]   55h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TRIM Multiplier                    | TRIM MULT               | 1 | [232]     | 2h            |

| Secure TRIM Multiplier   SEC_ERASE_MULT   1   (230)   FFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ·                                  | SEC FEATURE SUPPORT     | 1 |           |               |

| Secure TRIM Multiplier   SEC_TRIM_MULT   1   (229)   FFh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                    |                         | 1 |           | +             |